## Asynchronous SAR ADC with self-timed track-and-hold

Sunghyun Bae, ¹ D Sewon Lee, ¹ D Siheon Seong, ² D Jiwon Woo, ² and Minjae Lee¹, 2, ☒ D

This paper presents an asynchronous SAR ADC featuring a self-timed track-and-hold (STH) architecture. The design aims to address the common timing issue of divider-based clock generation, where the fixed-time track-and-hold (FTH) period often results in incomplete conversions due to prolonged conversion times time due to comparator metastability. To alleviate the degradation of the ENOB induced by these delays, the proposed STH method is introduced so that more conversion period is secured without requiring a high-speed input clock. Based on measurements, the proposed STH method achieves up to 0.7 bit improvement over the conventional FTH approach as conversion time increases.

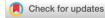

Introduction: SAR ADCs are widely used due to their medium-to-high resolution, low power consumption, and compact size [1-4]. Conventional asynchronous topology enables faster operation by the self-timed mechanisms [5-8], as shown in Figure 1a. These mechanisms comprise track-and-hold (T/H) and conversion periods [4], with the endpoint of each conversion dynamically determined for every sampling instance [5-8]. Typical asynchronous architectures require a high-frequency input clock to generate a predetermined T/H period [9, 10], and each clock cycle also needs a margin to account for clock jitter [11]. To alleviate speed limitations, alternative techniques like tapered clock generation are available [12]. For instance, to achieve a 25% T/H duty cycle, the input clock needs to be four times faster than the sampling clock frequency (fs). It is challenging to generate optimal T/H periods because faster input clocks are required to generate accurately controlled periods. Additionally, the asynchronous SAR ADC may lose LSB conversions because of longer decision time in comparators' metastability, as shown in Figure 1b [13]. This paper presents a sampling clock generation without requiring higher input clock frequency and increases the timing margin in LSB conversions with a self-timed clocking scheme.

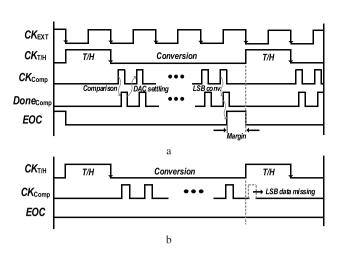

*Proposed architecture:* Figure 2a shows illustrates the overall SAR ADC configuration, incorporating both the traditional FTH and our proposed STH modes. For example, the FTH method utilizes a clock that is four times faster to generate a T/H with a 25% duty cycle. As a result, to match the sample rate of the proposed STH method, FTH requires a four times faster clock. In the conventional clock generation scheme, *EOC* conversion must happen before the T/H starts as shown in Figure 1a otherwise the LSB conversion data is lost as shown in Figure 1b.

The STH mode operates through a variable T/H clock  $(CK_{T/H,var})$ generation, as shown in Figure 2b. After the LSB conversion completes, either  $D_{OP}$ <0> or  $D_{ON}$ <0> becomes high. This transition generates an EOC signal two clock-to-Q delays later. The high state of EOC then triggers an additional clock pulse known as valid as shown in Figure 2b. This valid activates  $CK_{T/H,var}$  to high after one cycle comparator clock delay, so that the longer conversion time is secured in the case of longer decision time in comparators. When the external clock  $(CK_{EXT})$  transitions to zero, both EOC and  $CK_{T/H,var}$  are reset to zero as shown in Figure 2c. Even if the OR gate enters a metastable state, the system effectively mitigates this issue by delaying the start of the next T/H cycle to obtain more time to resolve. The extra circuitry may introduce some delay, but the ability to dynamically adjust the T/H period for the next cycle could actually make the system faster. Metastability mainly occurs during LSB conversions due to small input differences. Nevertheless, the STH method can yield improvements of more than 1 LSB in the case of a large T/H period design.

Fig. 1 Timing diagram of the asynchronous SAR ADC

Fig. 2 Proposed asynchronous SAR ADC

Figure 3 shows simulated waveforms. Figure 3a displays T/H clock overlap due to various delay codes, simulating different conversion times. Unlike FTH, STH adjusts its T/H period based on conversion end times. Figure 3b demonstrates that STH successfully tracks input signals (VINP and VINN) even with a duty ratio below 25%, contrasting with FTH's divide-by-four period. As a result, STH maintains all conversion data while FTH loses one LSB. However, STH faces challenges in Region C due to insufficient tracking time.

Measurement result: The proposed SAR ADC, fabricated using a 55-nm ULP CMOS process, operates at a sampling rate of 1MS/s and achieves a Figure of Merit (FoM) of 19.59 fJ/conv-step. Figure 4 displays the die photograph of the ADC. The active area of the ADC measures  $0.099 \ mm^2$ , with a power consumption of  $43\mu W$  under a 1.2V supply voltage. This ADC performs 13-bit conversions with 15 total conversion cycles, of which two bits are used for redundancy. ADC employs a unit capacitor of 0.5 fF with MoM structure capacitors and features a two-stage dynamic comparator with a pre-amplifier and a cross-coupled

<sup>&</sup>lt;sup>1</sup>School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology, Gwangju, South Korea

<sup>&</sup>lt;sup>2</sup>R&D Department, Aconic Inc., Gwangju, Republic of Korea

E-mail: minjae@gist.ac.kr

Fig. 3 Simulation waveform of the proposed STH

Fig. 4 Chip photograph

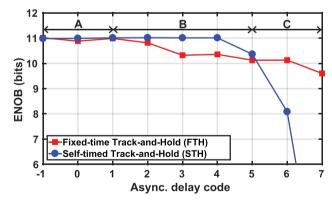

Fig. 5 Measured ENOB according to asynchronous delay code

latch step [1]. The delay cell for asynchronous clock generation has a delay step of approximately 800 ps and controls the DAC settling delay for ENOB performance comparison. The full-scale signal amplitude is applied as  $0.8\ V_{pp}$  centered around a common-mode voltage  $V_{CM}=0.6\ {\rm V}$ .

Figure 5 shows the measured ENOB of FTH and STH as conversion period is increased by controlling delay code, and there are three regions according to performance. Region A indicates that all the con-

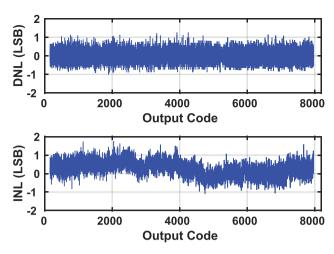

Fig. 6 Measured DNL/INL of the proposed self-timed T/H

Fig. 7 Measured FFT with FTH and STH

Table 1. Measured performance of FTH and STH modes

|            | Conventional FTH | Proposed STH |

|------------|------------------|--------------|

| ENOB [bit] | 10.4             | 11.1         |

| SNDR [dB]  | 64.1             | 68.8         |

| SFDR [dB]  | 74.6             | 84.6         |

versions performed with sufficient timing margins, resulting in similar ENOB performance for FTH and STH. Region B shows a situation in which the decision time is increased, and the timing margin becomes gradually insufficient in existing FTH methods. This results in a loss of LSB data and poor ENOB performance in traditional FTH methods. On the other hand, the proposed STH borrows the conversion time from the T/H period in the next sample, so there is no performance degradation. Region C has an excessively short T/H period in the proposed TH scheme, resulting in resulting in rapid performance degradation. Therefore, to avoid such performance degradation in Region C, the minimum T/H period must be secured.

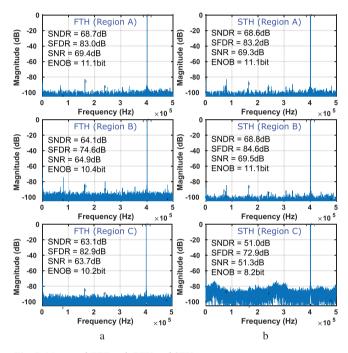

Figure 6 shows the DNL/INL performance of +1.2/-1.0 and +1.7/-1.1 LSB. Figure 7 shows measured six different FFT results obtained under varying delay codes, indicating that in Region B, the ENOB for FTH declines by 0.7 bits due to insufficient conversion time, while STH maintains an ENOB of 11.1 bits. Table 1 summarizes the comparisons of

Table 2. Performance comparison with the SAR ADCs

|                         | This Work | [14]    | [15]  | [16]  |  |

|-------------------------|-----------|---------|-------|-------|--|

| Technology [nm]         | 55        | 40      | 65    | 110   |  |

| Supply voltage [V]      | 1.2       | 1.1     | 0.85  | 0.9   |  |

| Sample rate [MS/s]      | 1.0       | 1.0     | 1.0   | 1.0   |  |

| Resolution [bits]       | 13        | 12      | 13    | 12    |  |

| SNDR [dB]               | 68.8      | 68.1    | 66.4  | 68.3  |  |

| SFDR [dB]               | 84.6      | 100.4   | 85.2  | 82.0  |  |

| ENOB [bit]              | 11.1      | 10.77   | 10.4  | 11.05 |  |

| DNL [LSB]               | 0.83      | -       | -     | 0.29  |  |

| INL [LSB]               | 1.89      | 1.8@16b | -     | 0.55  |  |

| Area [mm <sup>2</sup> ] | 0.099     | 0.073   | 0.027 | 0.079 |  |

| Power $[\mu W]$         | 43        | 31.1    | 45.2  | 24    |  |

| FoM [fJ/convstep]       | 19.59     | 15      | 34.64 | 11.7  |  |

ENOB, SNDR, and SFDR under a delay code of 4, assuming Region B. The overall performance for the SAR ADCs are summarized in Table 2.

Conclusion: This paper introduces a simple and effective STH method that enhances the timing margin for the conversion period without needing a high-speed input clock. When compared to the traditional FTH method with the proposed method, the proposed variable method consistently yields superior ENOB performance across a longer range of conversion periods.

Author contributions: Sunghyun Bae: Conceptualization, data curation, formal analysis, investigation, methodology, visualization, writing - original draft, writing - review and editing. Sewon Lee: Data curation, resources. Siheon Seong: Data curation, resources. Jiwon Woo: Data curation, resources. Minjae Lee: Supervision.

Acknowledgements: This work was supported by the Commercializations Promotion Agency for R&D Outcomes (COMPA) grant funded by the Korea Government (MSIT) (No. 20211500). The EDA Tool was supported by the IC Design Education Center (IDEC, Korea).

${\it Conflict of interest statement:} \ \ {\it The authors declare no conflict of interest.}$

Data availability statement: Data openly available in a public repository that issues datasets with DOIs.

© 2023 The Authors. *Electronics Letters* published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology.

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

Received: 18 July 2023 Accepted: 7 November 2023

doi: 10.1049/ell2.13026

## References

- Harpe, P., Cantatore, E., van Roermund, A.: A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step. *IEEE J. Solid-State Circuits* 48(12), 3011–3018 (2013)

- 2 Ding, M., et al.: A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration. *IEEE J. Solid-State Circuits* 52(2), 423– 432 (2017)

- 3 Liu, C.C., et al.: A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. *IEEE J. Solid-State Circuits* 45(4), 731–740 (2010)

- 4 Ju, H., Lee, M.: A 13-bit 3-MS/s asynchronous SAR ADC with a passive resistor based loop delay circuit. *Electronics* **8**(3), 262 (2019)

- 5 Yu, A., et al.: Understanding metastability in SAR ADCs: Part II: Asynchronous. *IEEE J. Solid-State Circuits* **11**(3), 16–32 (2019)

- 6 Chung, Y.H., Yen, C.W.: A pvt-tracking metastability detector for asynchronous adcs. In: 2016 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1462–1465. IEEE, Piscataway (2016)

- 7 Cao, S., Wang, C., Zhang, L., Luo, M., Yan, W., Gong, Y.: A fully integrated 10-bit 100 ms/s sar adc with metastability elimination for the high energy physics experiments. *Nucl. Instrum. Methods. Phys. Res. A* 978, 164415 (2020)

- 8 Shikata, A., et al.: A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS. *IEEE J. Solid-State Circuits* 47(4), 1022–1030 (2012)

- 9 Tsai, Y.H., Liu, S.I.: A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 30(7), 905–914 (2022)

- 10 Chen, C.H., et al.: Multi-step extended-counting analogue-to-digital converters. *Electron. Lett.* 49(1), 30–31 (2013)

- 11 Chen, S.W.M., Brodersen, R.W.: A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13- $\mu$ m CMOS. *IEEE J. Solid-State Circuits* **41**(12), 2669–2680 (2006)

- 12 Janke, D., et al.: A 9-Bit 10-MHz 28- μ W SAR ADC using tapered bit periods and a partially interdigitated DAC. *IEEE Trans. Circuits Syst. II Express Briefs* 66(2), 187–191 (2019)

- Waters, A., Muhlestein, J., Moon, U.K.: Analysis of metastability errors in conventional, LSB-First, and asynchronous SAR ADCs. *IEEE Trans. Circuits Syst. I Regul. Pap.* 63(11), 1898–1909 (2016)

- 14 Shen, J., et al.: A 12-Bit 31.1- μ W 1-MS/s SAR ADC with on-chip input-signal-independent calibration achieving 100.4-dB SFDR using 256-fF sampling capacitance. *IEEE J. Solid-State Circuits* 54(4), 937–947 (2019)

- 15 Yoshioka, K., Ishikuro, H.: A 13b SAR ADC with eye-opening VCO based comparator. In: ESSCIRC 2014-40th European Solid State Circuits Conference (ESSCIRC), pp. 411–414. IEEE, Piscataway (2014)

- 16 Chung, Y.H., Wu, M.H., Li, H.S.: A 24μW 12b 1MS/s 68.3dB SNDR SAR ADC with two-step decision DAC switching. In: Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, pp. 1–4. IEEE, Piscataway (2013)