# Recoverable Electrical Breakdown Strength and Dielectric Constant in Ultralow-k Nanolattice Capacitors

Min-Woo Kim,<sup>†,§</sup> Max L. Lifson,<sup>‡,§</sup> Gallivan A. Rebecca,<sup>‡</sup> Julia R. Greer,<sup>\*,‡</sup> and Bong-Joong Kim<sup>\*,†</sup>

Supporting Information

ABSTRACT: The dielectric reliability of low-k materials during mechanical deformation attracts tremendous attention, owing to the increasing demand for thin electronics to meet the ever-shrinking form factor of consumer products. However, the strong coupling between dielectric/electric and mechanical properties limits the use of low-k dielectrics in industrial applications. We report the leakage current and dielectric properties of a nanolattice capacitor during compressive stress cycling. Electrical breakdown measurements during the stress

cycling, combined with a theoretical model and in situ mechanical experiments, provide insights to key breakdown mechanisms. Electrical breakdown occurs at nearly 50% strain, featuring a switch-like binary character, correlated with a transition from beam bending and buckling to collapse. Breakdown strength appears to recover after each cycle, concomitant with nanolattice's shape recovery. The compressive displacement at breakdown decreases with cycling due to permanently buckled beams, transforming the conduction mechanism from Schottky to Poole-Frankel emission. Remarkably, our capacitor with 99% porosity,  $k \sim 1.09$ , is operative up to 200 V, whereas devices with 17% porous alumina films breakdown upon biasing based on a percolation model. Similarly with electrical breakdown, the dielectric constant of the capacitor is recoverable with five strain cycles and is stable under 25% compression. These outstanding capabilities of the nanolattice are essential for revolutionizing future flexible electronics.

KEYWORDS: Nanolattice capacitor, electrical breakdown, dielectric constant, buckling, Poole-Frenkel emission

$\Gamma$  he development and integration of reliable low-kmaterials are key challenges for next generation interconnect<sup>1,2</sup> and wireless communication<sup>3-6</sup> technologies. Lowering the dielectric constant k, which has commonly been enabled by introducing pores into the dielectric material, 7,8 decreases the resistance-capacitance (RC) delay, reduces power consumption, reduces cross-talk between nearby interconnects in integrated circuits (ICs), 9-11 and increases the bandwidths in antennas by preventing surface wave propagation.<sup>12</sup> Lowering the k through increasing porosity often degrades intrinsic electrical reliability<sup>13</sup> and leads to a higher leakage current and lower dielectric breakdown voltages along with other physical properties including mechanical integrity, thermal stability, and dielectric loss.<sup>7,8</sup> Despite extensive research efforts, no material has successfully broken the negative link between the physical and dielectric properties of the materials.<sup>7,8</sup>

The electrical and dielectric reliabilities of low-k materials under stress require characterization due to the increasing popularity of thin and flexible electronic devices in a wide variety of technological areas, such as batteries, <sup>14–18</sup> transistors, <sup>19–21</sup> electrodes, <sup>22,23</sup> displays, <sup>24</sup> biosensors, <sup>25–29</sup> and biomedical instruments. <sup>30–32</sup> These devices are required to undergo large mechanical deformation in uses that include

bending, stretching, twisting, and folding, while maintaining the reliable high performance of the devices. These reliabilities are of great concern in manufacturing of the ICs, particularly the cool-down procedure in the back-end-of-line (BEOL) processes that induce thermal expansion.<sup>33</sup> Porous low-k films have shown a large degradation in both reliabilities under mechanical stress, and after unloading the stress, both the leakage current and the dielectric constant were not recovered.34

A vertical-type three-dimensional (3D) nanoarchitected hollow-beam alumina capacitor demonstrated a substantial improvement of physical properties and achieved the lowest reported k of 1.06–1.10 at 1 MHz in the 1% density regime.  $^{35}$ This architected capacitor emerges as a potential solution for current low-k materials because it provided stable k values over the voltage range of -20 to 20 V and a frequency range of 100 kHz to 10 MHz, with excellent mechanical properties such as a Young's modulus of 30 MPa, a yield strength of 1.07 MPa, a nearly full shape recoverability after >50% compressions, and

Received: June 4, 2019 Revised: July 11, 2019 Published: July 12, 2019

<sup>&</sup>lt;sup>†</sup>School of Materials Science and Engineering, Gwangju Institute of Science and Technology (GIST), 123 Cheomdangwagi-ro, Buk-gu, Gwangju 61005, Korea

<sup>&</sup>lt;sup>‡</sup>Division of Engineering and Applied Science, California Institute of Technology, Pasadena, California 91125, United States

an outstanding thermal stability with a thermal coefficient of dielectric constant (TCK) of  $2.43 \times 10^{-5}$  K<sup>-1</sup> up to 800 °C.<sup>35</sup>

In this work, we fully and for the first time investigated the electrical and dielectric properties of these nanolattice capacitors under electrical and mechanical stress. We probed the leakage current of a 8  $\mu$ m-tall hollow-tube alumina nanolattice capacitor with octet architecture, comprised of a 8  $\mu$ m-wide layer of unit cells subjected to cyclical loading to strains of 0–nearly 50%. Quantifying the conditions that resulted in electrical breakdown combined with a phenomenological model provides insights into the uniquely reliable response of such nanoarchitected materials under mechanical strain, including the high strength, binary nature, recoverability and degradation of the electrical breakdown, and recoverability of dielectric properties.

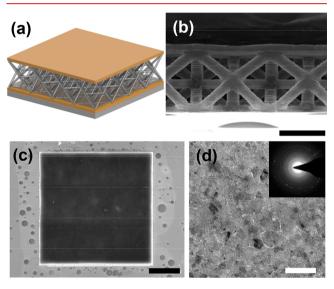

We fabricated vertical-type nanolattice capacitors to probe the electrical properties of nanoarchitected materials under stress. Figure 1a shows a schematic depicting the nanolattice

**Figure 1.** Architected alumina nanolattice capacitor, (a) Schematic of the octahedron nanolattice capacitor with top and bottom electrode layers. (b, c) Side- and top-view SEM images of a fabricated nanolattice capacitor (an 8  $\mu$ m single unit cell layer, 8  $\mu$ m sample height, and 350 × 350  $\mu$ m² planar top), respectively. The scale bars of Figure 1b,c are 5 and 100  $\mu$ m, respectively. (d) TEM bright-field image of an alumina tube. The corresponding SAD pattern is shown in the inset of the image. The scale bar is 50 nm.

capacitor with a single 8  $\mu$ m octet geometry unit cell layer with a monolithic top plate, fabricated by two-photon lithography <sup>36</sup> as detailed in Methods. The planar top area and height of the nanolattice are 350 × 350  $\mu$ m<sup>2</sup> and 8  $\mu$ m, respectively, as exhibited in Figure 1b,c. A bright-field (BF) transmission electron microscopy (TEM) image and the corresponding selective area diffraction (SAD) pattern of an alumina tube of the nanolattice indicate that the nanolattice is mostly comprised of an amorphous matrix with nanograins in the size range of 2–10 nm.

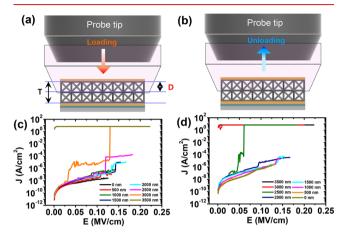

To understand the effect of nanolattice strain on the electrical properties, we measured the electric breakdown field  $(E_{\rm BD})$  and current density  $(J_{\rm BD})$  of a nanolattice capacitor, while applying a compressive strain along the top of the capacitor using a specially designed tungsten probe tip. The cross-sectional area of the 550  $\mu{\rm m}$  diameter tip is approximately 2 times larger than the top area of the capacitor,

whose surface roughness is  $\pm 20$  nm as measured by atomic force microscopy (AFM) (Figure S1), which enabled conformal contact and homogeneous displacement. During the experiments, the strain was gradually increased as the underlying substrate moved upward with a step size of 500 nm, while the tip maintained its position of full top contact. After reaching a displacement of 3500 nm, the sample was unloaded to remove all strain over the same increments until the sample reached its initial height (Figure 2a,b). The breakdown field

Figure 2. Electrical reliability tests for the first stress cycle. (a, b) Schematics of the electrical reliability tests of the nanolattice capacitor under loading (compressive stress) and unloading (removing the stress), respectively. Note that the T is the initial height of sample and D is the displacement of the tungsten probe. (c, d) Representative current density (J) vs electric field (E) plots of the nanolattice capacitor under various displacements during loading (c) and unloading (d) the stress, respectively.

was measured as the current density abruptly jumps, and can be classified as either a partial breakdown, marked by the first sudden increase in current of at least 1 order of magnitude, or a full breakdown, which indicates the onset of a metallic conducting state. We observed only partial breakdown events for all displacements below 2500 nm, with slight and gradual increases in  $J_{\rm EBs}$  (up to  $7\times 10^{-5}~\rm A/cm^2$ ) for the electric field values beyond  $E_{\rm BDs}$  and overall J as the displacement increases. Displacements greater than 2500 nm resulted in decreases in  $E_{\rm BD}$  and drastic increases in  $J_{\rm BD}$  up to  $7~\rm A/cm^2$ , (the compliance current for this experiment), which indicate full breakdowns (Figure 2c). It is evident that both trends are recovered upon unloading, which demonstrates that the capacitor regains the ability to maintain a voltage across its electrodes.

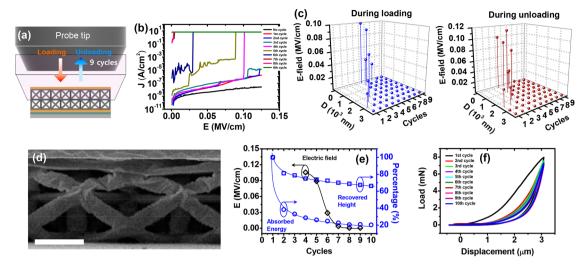

To understand the evolution of the electrical response to mechanical deformation, we mechanically cycled the capacitors nine times. Figure 3b shows the E vs J plots of the unloaded capacitor after their return to initial height from each cycle. No breakdown events were observed before or after the first cycle due to the maximum voltage limit of the experiment. Partial breakdowns occurred in the second and third cycles, while full breakdowns were observed in the fourth cycle and beyond. Figure 3c depicts a 3D representation of the full  $E_{\rm BD}$  with displacement and cycle number. Data points do not exist for experiments where electrical breakdowns were not observed during voltage sweeps. Points that equal zero designate short circuits that led to full breakdowns. Images in Figure 3d show

Figure 3. Electrical reliability tests of the nanolattice capacitor for repeated stress cycles and their analyses. (a) A schematic of the electrical reliability tests for 9 cycles. (b) The J vs E plots at the initial height (with no displacement) after each of the cycles. (c) The profiles of full-breakdown fields during loading and unloading processes as a function of the displacement (D) and cycle. (d) The cross-sectional SEM image of the nanolattice capacitor after 9 compression cycles. The scale bar is 4  $\mu$ m. (e) The normalized absorption energy, recovered height, and full-breakdown fields as a function of the cycles. (f) Load—displacement plots of the capacitor showing the recoverability of their shape with an initial large drop in energy absorption, followed by a plateau, up to 3500 nm of displacement during the repeated cycles for 10 times.

that nonrecoverable deformation and cracks formed beyond the fourth cycle, where instantaneous breakdowns occurred.

It has been shown that DC conduction of Al<sub>2</sub>O<sub>3</sub> at high electric fields can be described by the space charge limited conduction (SCLC) model, 37,38 where electrons or holes are injected into the material via the electrodes and alter the local space charge distributions. Such conditions can create a conducting path within the material such that the local internal electric field exceeds the breakdown voltage of the material, and this conducting path can lead to global electrical breakdown of the material, characterized by a drastic increase in measured current. We developed a simplified phenomenological model with corresponding qualitative finite element analysis (FEA) maps to estimate the local electric field within the nanolattice capacitor. We modeled a stationary 2D slice of the hollow ceramic nanolattices with the voltage difference between the terminal and ground as 100 V, equal to the condition of Figure 2c,d. The terminal and ground were designated as the top and bottom boundaries, respectively, and were assigned the default material parameters for gold. The 10 nm shell members were designated as alumina with an  $\varepsilon_{\rm r} = 8.39$ All remaining components are designated as air ( $\varepsilon_r = 1$ ). The model involves solving both Gauss' law and the electrical potential equations as follows:

$$\nabla D = \rho_{V} \tag{1}$$

$$E = -\nabla V \tag{2}$$

where D is the electric flux density,  $\rho_{\rm V}$ . is the volumetric charge density, E is the electric field, and V is the voltage.

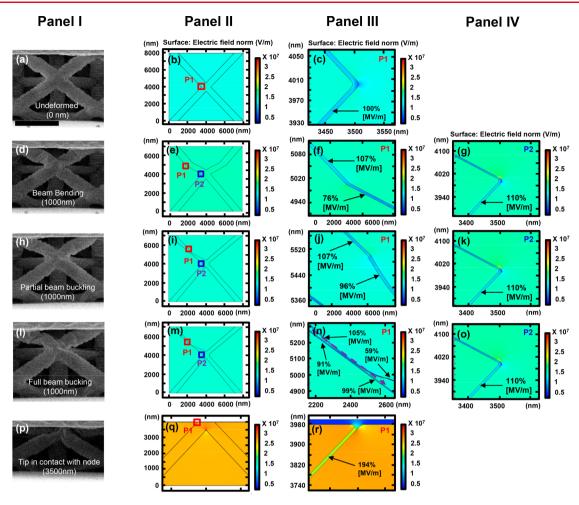

We modeled five geometric cases to match the mechanical deformation morphology that evolves during cyclic testing of the capacitor (Figure 4) (see details in Methods). Each case has a corresponding SEM image in panel I and an FEA image that shows the norm of the electric field in panel II. The areas marked by the red and blue rectangles on each image in panel II are magnified in panels III and IV, respectively. The initial undeformed case is illustrated in Figure 4a–c. The local electric field within the undeformed beam is uniform and

designated as 100%. We explored three intermediate deformation mechanisms: beam bending, partial beam buckling, and full beam buckling. The model for this regime uses 1000 nm of displacement, which qualitatively represents the cases of displacement between 0 and 3500 nm in the experiments. The first mechanism is beam bending (Figure 4d-g), where both walls of the hollow tube bend and remain roughly parallel. This model estimates the local electric field to be higher than the breakdown field above the point of bending in the shell and lower below this point. The lower half of the unit cell has a field that is 110% of the original, which is caused by reducing the plate separation at the same voltage. This does not lead to a continuous pathway of a higher electric field and thus is not likely a contributor to decreasing the required breakdown field. The second deformation case is partial beam buckling (Figure 4h-k), which gives rise to the similar effect as beam bending; the local electric field is 107% of the original field above the initiation of buckling and 96% of the initial field below. The lower half of the unit cell also has a field that is 110% of the original. Like, in the first case, there is no continuous pathway of an increased electric field, which would result in greater breakdown susceptibility. The final intermediate deformation case is full beam buckling (Figure 41-o), which can occur after repeated compression cycles where the hollow tube fails to recover its original shape. In this scenario, the higher electric field in the top shell above the wrinkling vertex comes into contact with the relatively unchanged electric field of the bottom shell below the vertex. Similar to the previous scenarios, the lower half of the unit cell has a field that is 110% of the original. This scenario creates a potential continuous pathway of an increased electric field, which can result in a lower effective breakdown strength. The fifth and final scenario describes the geometry at the maximum displacement of the experiment (Figure 4p-r). At this displacement, the top half of the unit cell is completely compressed, resulting in the conductive tip contacting the plane of nodes that are positioned at roughly half the height of the structure. This effectively removes the entire pathway along the top half of the structure and creates a direct pathway

Figure 4. FEA simulation results of the five representative geometric cases of the nanolattice capacitor in different regimes of compressive stress with matching images from in situ mechanical experiments. (a-c) Undeformed case at no displacement. (d-n) Three intermediate deformation cases occurring at 1000 nm of displacement as a representation for the cases of displacements between 0 to 3500 nm: (d-g) Beam bending, (h-k) partial beam buckling, and (l-o) full beam buckling cases. (p-r) Full displacement case at 3500 nm of displacement where the tip comes into contact with the halfway plane of nodes. The panels I and II show the cross-sectional SEM image corresponding to each case and the FEA image for the norm of the electric field. The panels III and IV show the magnified images that are marked by the red and blue rectangles, respectively, in panel II. The scale bar in Figure 4a is 4  $\mu$ m.

between the tip, the shell below the node, and the substrate. Additionally, the applied field reaches its maximum value, almost twice what was found in the undeformed case, due to the decreased plate separation.

This simple model lends insights into the three main experimental observations: (1) the binary character, (2) recoverability, and (3) degradation of the electrical breakdown. The binary nature (observation (1)) of the full-breakdown response within a cycle could be explained by the transition from beam bending and buckling to lattice collapse, which disrupts the continuous current pathway with an increased local electric field. Once the tip is in contact with the node halfway down the structure, a large increase in field as shown in the model leads to a full electrical breakdown. This suggests that within the first cycle the capacitor behaves as a switch; it either breaks down according to the structural and material breakdown strength or behaves as a short circuit once the tip reaches the node. No full breakdowns are observed before this displacement in the cycle, since there is no large increase in the internal electric field in a continuous conduction pathway through the structure. For the partial breakdowns that occur at displacements below 3000 nm in the first cycle (Figure 2c,d),

only some of the beams in the top half of the unit cell experience full beam buckling, which forms a limited number of continuous pathways, and the number of the beams increases with the displacement, as reflected by the increase in leakage currents at intermediate plateaus of electrical breakdown, partial electrical breakdowns (Figure 2c,d).

The recoverability of electrical breakdown (observation (2)) is correlated with the material regaining most of its breakdown strength after each cycle (Figure 3b). Hollow alumina nanolattices have been ubiquitously shown to recover structural shape, and the capacitor may be able to reverse its collapsed state upon recovery and break the continuous pathways that caused breakdown. We note that, despite the lattice recoverability, the overall current level increases with increasing the number of cycles, representing some damage might be accumulating in the junctions of the nanolattice. The displacement, at which electrical breakdown occurs (observation (3)), decreases with cycling. This observation could be explained by the accumulation of fully buckled beams, which cause continuous pathways of increased local electric fields. As each cycle introduces an increasing number of beams, which are fully buckled and no longer recover, the number of

Figure 5. Dielectric properties of the nanolattice capacitor measured before cycling, during loading of 2000 nm at the first strain cycle, during unloading of 2000 nm at the fifth strain cycle, and after the fifth strain cycle (no strain): (a-d) Capacitance density vs frequency plots. (e-h) Capacitance density vs voltage plots at frequencies of 100 kHz as well as 1 and 10 MHz.

pathways for breakdown increases and the electrical performance subsequently degrades.

Further expanding the correlation between the electrical breakdown behavior and mechanical degradation properties of the capacitor, Figure 3e shows the normalized energy dissipation, defined as the line integral along the stress-strain curve for a given cycle, normalized recovered height, and full  $E_{\rm BD}$  at zero displacement as a function of cycle number. Normalized recovered height characterizes the structure's shape recovery after stress is applied and energy dissipation is linked to the material's ability to relax stress. Both characteristics scale with structural deterioration as they both depend on defects accumulated during cycling. Figure 3e shows the energy dissipation and height recovery decrease by 61.6% and 18.8%, respectively, between the first and second cycles, during which no full electrical breakdown occurs. This steep mechanical signature is likely due to initial nodal fractures followed by subsequent hinge-like deformation (Figure S2). Subsequent cycles display marginal lowering of recoverability (approximately 10% and 20% for the normalized recovered height and energy dissipation, respectively, for the entire periods of second to 10th cycles), indicating that the primary permanent deformation occurs during the initial compression. A full electrical breakdown first occurred in the fourth cycle, and subsequently, the capacitor becomes completely short-circuited beyond the seventh cycle. Such discrepancy between mechanical and electrical breakdown behavior can be explained as follows. With increasing cycling, more beams in the top half of the unit cell form direct current pathways close to the nodes, which ultimately replicates the case at which the conducting tip is in contact with nodes, leading to an immediate breakdown at a low  $E_{\rm BD}$ . Beam buckling helps to prevent further fracture of nodes and tubes by relaxing the stress as exhibited in Figure 3d.<sup>36</sup> A sufficient number of nodal connections remain intact to enable the structure to recover its height and to preserve the amount of energy dissipation. To confirm this hypothesis, we measured the decrease in the height of the capacitor after 7 mechanical cycles with biasing up to 100 V. The cross-sectional SEM image (Figure S3) indicates the height decreases by about 25%, which is similar to the value when only 7 mechanical cycles are engaged as shown in Figure 3e. Therefore, electrical breakdown is facilitated by deterioration of beam structure

through buckling, while the mechanical degradation is linked to failure at the nodal regions.

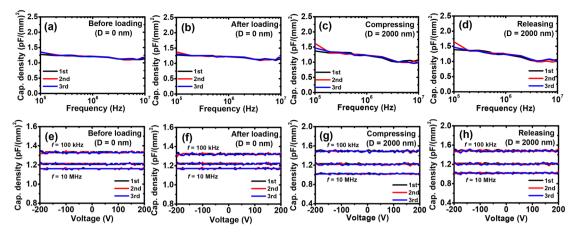

Examining and quantifying the effect of compressive stress on the dielectric properties of nanoarchitected capacitors that have been demonstrated to possess mechanical, thermal, and dielectric stability is of critical importance.<sup>35</sup> We measured the capacitance of an 8  $\mu$ m single unit cell layer nanolattice in this work using a Keithley 4200-SCS impedance analyzer, with 5 stress cycles (see details in Methods). Figure 5a-d shows capacitance density vs frequency plots of the fabricated sample before stress cycling, under loading of 2000 nm at the first cycle, under unloading of 2000 nm at the fifth cycle, and after the fifth stress cycle. The data conveys that all cases exhibit similar values with nearly constant capacitance densities over the frequency range of 100 kHz to 10 MHz at an applied bias of  $\pm 200$  V. The capacitance densities of the four cases are  $1.210 \pm 0.006$ ,  $1.223 \pm 0.006$ ,  $1.237 \pm 0.010$ , and  $1.220 \pm$ 0.006 pF/(mm)<sup>2</sup>, respectively, which equate to dielectric constants of  $1.094 \pm 0.005$ ,  $1.106 \pm 0.005$ ,  $1.118 \pm 0.010$ , and  $1.103 \pm 0.005$ , respectively (see details for calculating k in the Supporting Information). These results indicate that the dielectric constant is stable under loading of up to 2000 nm and fully recoverable up to 5 cycles, beyond which the measurements of capacitance fail due to high levels of leakage current (Figures 2c,d, Figure S5a,b, and Figure 3b).

Figure 5e—h shows capacitance densities of the four cases as a function of bias swept from -200 V to +200 V at frequencies of 100 kHz as well as 1 and 10 MHz. These plots show that the capacitance densities were stable, and the dielectric losses are below 0.061 throughout the range of frequencies and voltages used (Figure S4a—h). The C–V plots shown in Figure 5e—h were normalized by the relative capacitance as a function of applied voltage at varied frequencies to extract the voltage coefficients of capacitance (VCCs),  $(C-C_0)/C_0$ , where  $C_0$  is the capacitance density at zero bias (Figure S4i—l). These measurements revealed that the VCCs were virtually nonexistent, which implies that the nanolattice is stable over this voltage range. Measurements of nanolattice capacitance over 3 experiments produced approximately identical data, as conveyed in the plots in Figures 5 and S4.

To examine the dependence of compressive strain on full electrical breakdown, we doubled the applied voltage up to 200 V (the maximum bias of our system) with another nanolattice capacitor and observed that the full  $E_{\rm BD}$  decreases with an

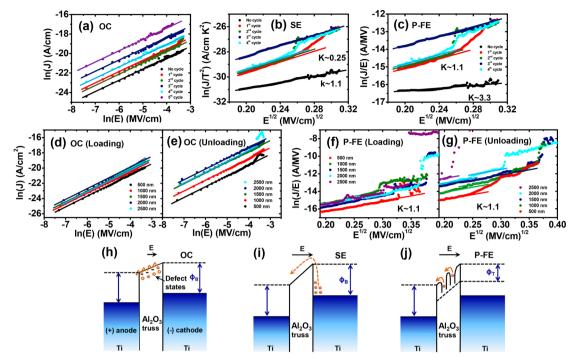

**Figure 6.** Conduction mechanisms of the nanolattice capacitor prior to full breakdowns: leakage data obtained before stress cycling and after the cycles shown in Figure 6a–c and those acquired during the cycles with varied displacements shown in Figure 6d–g. (a) Plots of the leakage current varying linearly with electric fields at 0–0.036 MV/cm (Ohmic conduction (OC)). (b, c) Plots of  $\ln(J/T^2)$  and  $E^{1/2}$  and  $\ln(J/E)$  and  $E^{1/2}$  beyond the Ohmic conduction regime. The former is for SE and the latter is for P-FE. (d, e) Plots of the leakage current varying linearly with electric fields at 0–0.036 MV/cm (Ohmic conduction (OC)). (f, g) Plots of  $\ln(J/E)$  and  $E^{1/2}$  beyond the Ohmic conduction regime. (h–j) Schematic illustrations of electrical conduction mechanisms of OC, SE, and P-FE, respectively.

increasing strain as shown in Figure S5c (see all of the data of Figure 2c,d and Figure S5a,b). By combining the known models of porosity (based on the percolation model)<sup>13</sup> and thickness dependence<sup>38</sup> (see the Supporting Information for deriving the integrated equation) with the previous experimental results of porous alumina films<sup>38</sup> (Figure S5d), we estimated the porosity value (of the alumina film normalized in the same thickness with our capacitor, 8  $\mu$ m) of 16.71%, at which the full  $E_{\rm BD}$  becomes zero and above which the device with this porous material should instantly breakdown when electric field is applied. Also, the alumina film with a 16.71% porosity has a k value of 6.83 as calculated by the model in ref 35; see the Supporting Information. However, it is remarkable that our nanolattice capacitor with a ~99% porosity (when uncompressed) does not breakdown up to 0.25 MV/cm (Figure S5a,b), representing an exceptionally strong breakdown strength, while maintaining an extremely small k of ~1.10, which is electrically stable and mechanically recoverable (Figure 5 and Figure S4).

In determining the conduction mechanisms of the capacitor before full breakdown occurs, we first focus on the data at zero displacement before and after compression cycles. Figure 3b shows two distinct regions of *E* before full electrical breakdown. In the low electric field range (0–0.036 MV/cm), the current density linearly increases with electric field, indicating Ohmic conductions (OCs) (Figure 6a, see the definition of the Ohmic conduction mechanism in the Supporting Information), and mechanical cycling leads to a higher conductivity. This increase in conductivity might be caused by a greater number of electronic defect states with mechanical cycles, forming shallower traps (efficient sites for electrons to hop; see the schematic in Figure 6h) that generate

a current even at room temperature. 40 Beyond the Ohmic regime, the Schottky emission (SE) dominates the conduction mechanisms for the leakage current before the first cycle (Figure 6b), and the Poole-Frankel emission (P-FE) controls the mechanism after the first cycle (Figure 6c). These mechanisms are confirmed by linear correlations between  $ln(I/T^2)$  and  $E^{1/2}$  for SE and ln(I/E) and  $E^{1/2}$  for P-FE. The effective dielectric constant, k of  $\sim 1.07 \pm 0.05$  calculated by this method is consistent with the measured value shown above, for the SE mechanism before loading and the P-FE mechanism after loading. (See the definitions of the SE and P-FE mechanisms in the Supporting Information.) Since SE defines a mechanism for "electrode-limited conduction" and P-FE describes "bulk-limited conduction" as shown in Figure 6i,j, 33,41 the transition from SE to P-FE indicates the creation of trap (defect) states in the capacitor during the cycle. The number of states accumulates with the cycle, leading to an increase in the y-intercept values of the plots after each cycle (Figure 6c). The identical trends are observed in the leakage current during loading. As exhibited in Figure 6d-g, the conduction initially shows Ohmic behavior (Figure 6d,e) followed by characteristics of the P-FE mechanism (Figure 6f,g) with the level of the current density gradually increasing as the displacement becomes larger. Similarly, this behavior is due to the increased conductivity that is attributed to the defect sites<sup>40</sup> and/or the strain under compression.

The investigation presented here provides critical insights into the unique electrical breakdown behaviors, conduction mechanisms, and dielectric properties of hollow alumina nanolattices under cyclic compressions to nearly 50% strain. We discovered that this material maintains a stable dielectric breakdown strength and recovers a substantial portion of its

breakdown strength for a given displacement within a few cycles. Similar trends were also observed in dielectric properties. These features could provide a pathway to increase resilience of devices that have to function in extreme environments. For example, such reversibility in both electrical and dielectric properties may offer opportunities to rescue data in memory after an electrical and/or mechanical failure without using complicated and expensive restoration processes and facilities. Finally, the simple model used in our work suggests that it may be possible to utilize the breakdown voltage as a diagnostic tool to characterize the mechanical integrity of architectural dielectric materials.

Methods. Sample Fabrication. Low-density octet geometry nanolattices composed of an 8  $\mu$ m unit cell and a monolithic top plate were designed in computer-aided design (CAD) software. Utilizing this code, IP-DIP 780 polymer nanolattice scaffolds were created using two-photon photolithography (TPL) direct laser writing (DLW) in the Photonic Professional TPL-DLW System (Nanoscribe GmbH) on Si wafers coated with titanium (12 nm) and gold (80 nm). These polymer nanolattices were then coated with a 10 nm thick atomic layer deposition (ALD) alumina film in a Cambridge Nanotech S200 ALD System using H2O and trimethylaluminum (TMA) precursors. The interior polymer nanolattice scaffold was then removed by using a focused ion beam (FIB) system (FEI Versa 3D) to remove portions of the outer alumina coating and placing the sample in a Diener Zepto oxygen plasma system for several hours. The top electrode was formed by depositing titanium (12 nm) followed by gold (80 nm) on top of the structure. This results in a vertical capacitor with an interior dielectric material composed of a hollow 3D ceramic nanolattice. The maximum 2D size for each nanolattice was typically 350  $\mu$ m  $\times$  350  $\mu$ m.

Electrical Measurements. The measurements for dielectric and electrical properties of 3D ceramic nanolattice were carried out with a semiconductor characterization system (Keithly 4200-SCS connected to a 4210-CVU multi frequency capacitance-voltage unit). For dielectric properties, a voltage range of -200 to 200 V and a frequency range of 100 kHz to 10 MHz were applied, while, for electrical properties, a range of voltages up to 200 V was engaged. To avoid applying stress to the nanolattice from contact and from thermal expansion of the material during the impedance measurements, we used flexible thin tungsten hair pins (diameter = 0.4  $\mu$ m) and a specially designed stage, which controls its height with a step of 100 nm, allowing us to monitor the measurement using a highresolution optical microscope (OM). The resolution of the OM is 300 nm. To effectively measure the electrical reliability under stress, we used a rigid tungsten tip that can measure electricity with simultaneously giving compressive stress to the nanolattice. We performed a voltage sweep at 0.16 V/s, while measuring the current at each displacement. To confirm the tip does not significantly press the nanolattice at the condition of no displacement, we compared the currents measured by the rigid and the flexible tips in the range of voltages from 0 to 200 V and found that the two currents are similar in a range of deviations of  $\pm 5\%$  and both cases show Ohmic conduction.

Mechanical Measurement. Energy absorption and recovery height measurements were performed by cyclically compressing nanolattice capacitor structures quasistatically using a flat punch tip in an in situ InSEM Nanomechanical Module (Nanomechanics, Inc.) attached to a Quanta SEM (Thermo-

Fisher Scientific) to 3500 nm of maximum displacement for 10 cycles.

Modeling for Electrical Reliability. COMSOL multiphysics 5.3 (COMSOL Inc.) using the electrostatics package was utilized following the configuration described in the text.

## ASSOCIATED CONTENT

# **S** Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nanolett.9b02282.

A thorough description of the dielectric constant, VCCs, an analytical model to calculate the dielectric constant using relative density, conduction mechanisms, a model integrating the dependence of porosity and thickness on breakdown strength, and additional figures (PDF)

## AUTHOR INFORMATION

# **Corresponding Authors**

\*E-mail: jrgreer@caltech.edu. \*E-mail: kimbj@gist.ac.kr.

#### ORCID ®

Bong-Joong Kim: 0000-0002-5335-4342

## **Author Contributions**

§M.-W.K. and M.L.L. contributed equally to this work.

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

B.-J.K. and J.R.G. acknowledge financial support from the "GIST-Caltech Research Collaboration" grant funded by the GIST in 2019. Portions of this work were conducted in the Lewis lab at Caltech.

## REFERENCES

- (1) Baker, R. J. CMOS Circuit Design, Layout, and Simulation, 3rd ed.; Wiley-IEEE Press: Hoboken, NJ, 2010.

- (2) Plummer, J. D.; Deal, M. D.; Griffin, P. D. Silicon VLSI Technology: Fundamentals, Practice, and Modeling; Prentice Hall: London, 2000.

- (3) Sebastian, M. T. Dielectric Materials for Wireless Communication; Elsevier, 2010.

- (4) Dernovsek, O.; Eberstein, M.; Schiller, W. A.; Naeini, A.; Preu, G.; Wersing, W. J. Eur. Ceram. Soc. 2001, 21, 1693.

- (5) Xia, Q.; Zhong, C.-W.; Luo, J. J. Mater. Sci.: Mater. Electron. 2014, 25, 4187.

- (6) Ren, L.; Zhou, H.; Li, X.; Xie, W.; Luo, X. J. Alloys Compd. 2015, 646, 780.

- (7) Shamiryan, D.; Abell, T.; Iacopi, F.; Maex, K. Mater. Today 2004,

- (8) Farrell, R.; Goshal, T.; Cvelbar, U.; Petkov, N.; Morris, M. A. Electrochem. Soc. Interface 2011, 20, 39.

- (9) Croes, K.; Pantouvaki, M.; Carbonell, L.; Zhao, L.; Beyer, G. P.; Tőkei, Z. *Int. Reliab. Phys. Symp.* **2011**, 2F.3.1–2F.3.7.

- (10) Gupta, T. Copper Interconnect Technology; Springer Science & Business Media, 2010.

- (11) Maex, K.; Baklanov, M. R.; Shamiryan, D.; lacopi, F.; Brongersma, S. H.; Yanovitskaya, Z. S. J. Appl. Phys. 2003, 93, 8793.

- (12) Pribetich, J.; Ledee, R.; Kennis, P.; Pribetich, P.; Chive, M. Electron. Lett. 1988, 24, 1464.

- (13) Ogawa, E. T.; Kim, J.; Haase, G. S.; Mogul, H. C.; McPherson, J. W. 41st Annual International Reliability Physics Symposium, Dallas, TX, 2003, p 166.

(14) Chen, Z.; To, J. W. F.; Wang, C.; Lu, Z.; Liu, N.; Chortos, A.; Pan, L.; Wei, F.; Cui, Y.; Bao, Z. Adv. Energy Mater. **2014**, *4*, 1400207.

- (15) Lin, H.; Weng, W.; Ren, J.; Qiu, L.; Zhang, Z.; Chen, P.; Chen, X.; Deng, J.; Wang, Y.; Peng, H. Adv. Mater. 2014, 26, 1217.

- (16) Gwon, H.; Hong, J.; Kim, H.; Seo, D.-H.; Jeon, S.; Kang, K. Energy Environ. Sci. 2014, 7, 538.

- (17) Chen, L.; Zhou, G.; Liu, Z.; Ma, X.; Chen, J.; Zhang, Z.; Ma, X.; Li, F.; Cheng, H.-M.; Ren, W. Adv. Mater. 2016, 28, 510.

- (18) Mo, R.; Rooney, D.; Sun, K.; Yang, H. Y. Nat. Commun. 2017, 8, 13949.

- (19) Pu, J.; Yomogida, Y.; Liu, K.-K.; Li, L.-J.; Iwasa, Y.; Takenobu, T. Nano Lett. **2012**, 12, 4013.

- (20) Lee, G.-H.; Yu, Y.-J.; Cui, X.; Petrone, N.; Lee, C.-H.; Choi, M. S.; Lee, D.-Y.; Lee, C.; Yoo, W. J.; Watanabe, K.; Taniguchi, T.; Nuckolls, C.; Kim, P.; Hone, J. ACS Nano 2013, 7, 7931.

- (21) Chortos, A.; Lim, J.; To, J. W. F.; Vosgueritchian, M.; Dusseault, T. J.; Kim, T.-H.; Hwang, S.; Bao, Z. *Adv. Mater.* **2014**, *26*, 4253.

- (22) Dong, S.; Xi, J.; Wu, Y.; Liu, H.; Fu, C.; Liu, H.; Xiao, F. Anal. Chim. Acta 2015, 853, 200.

- (23) Nagaraju, G.; Raju, G. S. R.; Ko, Y. H.; Yu, J. S. *Nanoscale* **2016**, 8, 812.

- (24) Liang, J.; Li, L.; Niu, X.; Yu, Z.; Pei, Q. Nat. Photonics 2013, 7, 817.

- (25) Mannsfeld, S. C. B.; Tee, B. C.-K.; Stoltenberg, R. M.; Chen, C. V. H.-H.; Barman, S.; Muir, B. V. O.; Sokolov, A. N.; Reese, C.; Bao, Z. Nat. Mater. **2010**, *9*, 859.

- (26) Yamada, T.; Hayamizu, Y.; Yamamoto, Y.; Yomogida, Y.; Izadi-Najafabadi, A.; Futaba, D. N.; Hata, K. Nat. Nanotechnol. **2011**, *6*, 296.

- (27) Kim, D.-H.; Lu, N.; Ma, R.; Kim, Y.-S.; Kim, R.-H.; Wang, S.; Wu, J.; Won, S. M.; Tao, H.; Islam, A.; Yu, K. J.; Kim, T.; Chowdhury, R.; Ying, M.; Xu, L.; Li, M.; Chung, H.-J.; Keum, H.; McCormick, M.; Liu, P.; Zhang, Y.-W.; Omenetto, F. G.; Huang, Y.; Coleman, T.; Rogers, J. A. *Science* 2011, 333, 838.

- (28) Choong, C.-L.; Shim, M.-B.; Lee, B.-S.; Jeon, S.; Ko, D.-S.; Kang, T.-H.; Bae, J.; Lee, S. H.; Byun, K.-E.; Im, J.; Jeong, Y. J.; Park, C. E.; Park, J.-J.; Chung, U.-I. *Adv. Mater.* **2014**, *26*, 3451.

- (29) Trung, T. Q.; Lee, N.-E. Adv. Mater. 2016, 28, 4338.

- (30) Kenry; Yeo, J. C.; Lim, C. T. Microsyst. Nanoeng. 2016, 2, 16043.

- (31) Lacour, S. P.; Benmerah, S.; Tarte, E.; FitzGerald, J.; Serra, J.; McMahon, S.; Fawcett, J.; Graudejus, O.; Yu, Z.; Morrison, B. *Med. Biol. Eng. Comput.* **2010**, *48*, 945.

- (32) Jeong, J.-W.; Kim, M. K.; Cheng, H.; Yeo, W.-H.; Huang, X.; Liu, Y.; Zhang, Y.; Huang, Y.; Rogers, J. A. Adv. Healthcare Mater. 2014, 3, 642.

- (33) Yang, Y.-L.; Young, T.-F.; Chang, T.-C.; Shen, F.-Y.; Hsu, J.-H.; Tsai, T.-M.; Chang, K.-C.; Chen, H.-L. Appl. Phys. Lett. 2013, 102, 102012

- (34) Cheng, Y.-L.; Huang, Y.-L.; Lee, C.-Y. ECS meeting abstracts, 2018-01, 1395.

- (35) Lifson, M. L.; Kim, M.-W.; Greer, J. R.; Kim, B.-J. Nano Lett. **2017**, 17, 7737.

- (36) Meza, L. R.; Das, S.; Greer, J. R. Science 2014, 345, 1322.

- (37) Talbi, F.; Lalam, F.; Malec, D. J. J. Phys. D: Appl. Phys. 2007, 40, 3803.

- (38) Neusel, C.; Jelitto, H.; Schmidt, D.; Janssen, R.; Felten, F.; Schneider, G. A. *J. Eur. Ceram. Soc.* **2015**, 35, 113.

- (39) Tapily, K.; Jakes, J. E.; Stone, D. S.; Shrestha, P.; Gu, D.; Baumgart, H.; Elmustafa, A. A. J. Electrochem. Soc. 2008, 155, H545.

- (40) Perera, R.; Ikeda, A.; Hattori, R.; Kuroki, Y. Microelectron. Eng. **2003**, 65, 357.

- (41) Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices; John Wiley & Sons, 2006.