Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2020.Doi Number

# An Ultra-Low Power, Adaptive All-Digital Frequency-Locked Loop with Gain Estimation and Constant Current DCO

Imran Ali<sup>1</sup>, Hamed Abbasizadeh<sup>2</sup>, (Member, IEEE), Muhammad Riaz ur Rehman<sup>1</sup>, Muhammad Asif<sup>1</sup>, Seong Jin Oh<sup>1</sup>, (Student Member, IEEE), Young Gun Pu<sup>1</sup>, (Member, IEEE), Minjae Lee<sup>3</sup>, Keum Cheol Hwang<sup>1</sup>, Youngoo Yang<sup>1</sup>, and Kang-Yoon Lee<sup>1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, 16419, South Korea

Corresponding author: Kang-Yoon Lee (klee@skku.edu).

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIP) (2014R1A5A1011478).

**ABSTRACT** In this paper, an ultra-low power, adaptive all-digital integer frequency-locked loop (FLL) with gain estimation and constant current digitally controlled oscillator (DCO) for Bluetooth low energy (BLE) transceiver in Internet-of-Things (IoT) is presented. For locking DCO frequency closest to the target channel, it adaptively controls capacitor banks with binary algorithm. With decrease in frequency resolution, DCO clock counts for each capacitor bank bit evaluation dynamically increases with the proposed technique for accurate frequency tracking. For compensating PVT variations and finding the BLE frequency deviation, the configurable digital DCO gain estimation is incorporated. The low power and constant current DCO operates in sub-threshold region and its power consumption is minimized by  $g_{ny}/I_D$  methodology optimization, constant current source for limiting current in DCO core through adaptive low-dropout regulator (LDO) and lowering the supply voltage. The proposed design is integrated in an ADPLL for BLE transceiver and it is fabricated with 1P6M TSMC 55 nm CMOS technology. The all-digital adaptive FLL is fully synthesizable and its area is 1800 μm<sup>2</sup> with 1.233 K gate count. The RMS current consumption is 103.32 μA from 1 V voltage supply with 103.32 µW power requirement. The experimental results reveal, DCO draws 480 µA current from 0.55 V supply voltage at center frequency. It has frequency resolution of 4.8 kHz. The oscillator PN, FOM and FOM<sub>T</sub> at 1-MHz offset frequency from 2.44 GHz carrier frequency are -122.85 dBc/Hz, 196.38 dBc/Hz and 208.19 dBc/Hz, respectively.

**INDEX TERMS** Adaptive controller, all-digital frequency locked loop, digitally controlled oscillator, gain estimation, constant current, LDO, ultra-low power, synthesizable

#### I. INTRODUCTION

Recently, the research on IoT devices for low power applications are increasing rapidly [1]-[4]. Ultra-low power, small area and low cost designs are the fundamental requirements for battery operated IoT devices. The BLE is very famous low power wireless connectivity standard in IoT applications. The BLE standard has been adopted as a popular solution for wireless connectivity in the IoT applications [5]-[8]. Similar to other wireless RF transceivers, BLE supported devices place a design challenges on the jitter performance, phase noise (PN) and modulation bandwidth of frequency locked loop. In RF transceiver applications, frequency

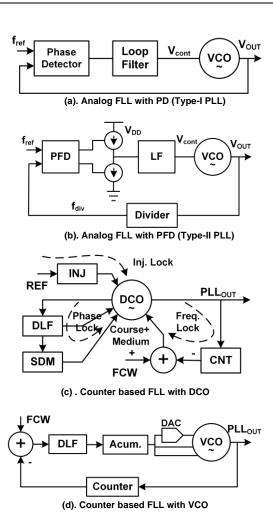

synthesizer, frequency multiplier and phase locked loop (PLL) demand circuits which bring oscillator frequency accurately closest to the target frequency. This essential task is performed by a frequency locked loop which is a vital circuit in RF devices and clock multipliers [9]-[11]. The type-1 PLL, depicted in Fig. 1(a) is composed of phase detector (PD), loop filter (LP) and voltage controlled oscillator (VCO) [12]. The FLL operation is performed in negative feedback loop with phase detector. It is simplest PLL due to single integrator in its control loop and high stability margin, unlike type-2 PLL [13]. However, if there is frequency drift, it cannot achieve zero average steady state phase error. Also, it has locking range

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093, USA

<sup>&</sup>lt;sup>3</sup>School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology, Gwangju, 61005, South Korea

FIGURE 1. Conventional FLL structures in PLL.

constraint, limited disturbance capability and significant reference spur due to persistent ripples on the VCO control line [12], [14]. In analog type-2 PLL, a phase and frequency detector (PFD) acts as analog FLL to bring VCO frequency closest to target frequency [15]-[17]. The PFD circuit compares the  $f_{ref}$  and  $f_{div}$  to generate up/down signals and tunes VCO frequency closest to the target frequency as shown in Fig. 1(b). Other than digital PFD technique, for the high frequency PLLs a voltage multiplier makes a trick by multiplying  $f_{ref}$  and  $f_{div}$  signals and getting a phase variation in DC to bring VCO frequency close to target frequency. These PFD circuits drive charge pump circuitry which cause an increase in area, power and lock time. The charge pump suffers from charge injection and clock feed through. However, type-2 PLL achieves zero average steady-state phase error under both frequency drifts and phase angle jumps, unlike type-1 PLL. Also due to the fast scaling in CMOS technologies, analog FLL circuits suffer from process, voltage and temperature (PVT) variations, loop filter encounters current mismatch, capacitor leakage and limited dynamic range which cause undesired performance in RF applications [18]. To overcome these limitations of PFD, a digital FLL is introduced [19]-[24]. A counter senses VCO/DCO output frequency and then the value is compared with a target frequency control word (FCW) as shown in the Fig. 1(c) and Fig. 1(d). It reduces power consumption by eliminating the charge pump and lock time reduces by introducing coarse and fine tracking strategies. Different oscillator topologies are investigated for improving phase noise (PN) with small area and low power. The single LC-tank oscillators are compact in size but shows inadequate PN. The multi-core VCOs enhance PN and figure-of-merit (FOM) at the cost of additional chip area. Recently, the single-core multi-LC-tank oscillator topologies are reported with compact size and high FOM for mm-wave wireless applications [25], [29].

The digital designs are proven robust to these PVT variations. This brings the idea of all digital FLL design for the wireless applications which meets strict frequency requirements of RF domain [22], [30]. All digital FLL offers significant advantages as compared to analog FLL. Analog FLL requires more area, strict supply voltage requirements, large loop filter capacitors and severe degradation in the performance due to capacitor leakage, current mismatch and PVT variations. Also implementation of state of the art loop calibration algorithms to encounter the PVT variations are not easily possible in analog domain [31]. While the all digital FLL offers advantages like small on chip area, fast settling, reconfigurable loop filter and portability to other process technologies. Current frequency tracking methodologies [19]-[25] use fixed DCO clock cycles for frequency locking closest to the target frequency. The PLL output frequency is measured and its difference from FCW is provided to DCO. The counting duration of DCO output significantly affects the accuracy and the lock time. In prior works, fixed counting duration is used which results large deviation of the locked frequency from the target one. To overcome this limitation, an adaptive FLL is proposed which efficiently adjust the counting mask automatically and significantly improves the locked frequency accuracy. This paper focuses on all-digital frequency loop for BLE applications in IoT devices. The major contributions of proposed design are as follows: (a) An adaptive all digital frequency loop in which DCO clock cycles are counted adaptively in an increasing order as the frequency resolution decreases to achieve DCO fine tuning, (b) DCO gain estimation which is the single bit frequency resolution for PVT variations and frequency-shift keying (FSK) modulation in RF transmitter, (c) Four different configurable operating modes for various control levels of DCO frequency and (d) Constant current DCO.

FIGURE 2. Reference frequency and DCO frequency relationship.

The rest of this paper is organized as follows: Section II presents the design of the proposed all-digital frequency-locked loop (ADFLL). The detailed description of the proposed architecture at building block levels is included in Section III; Section IV shows the simulation and experimental results; Finally, the paper is concluded in Section V.

#### II. PROPOSED ADAPTIVE ALL-DIGITAL FLL DESIGN

An all-digital phase locked loop structure is composed of integer and fractional loops. The fractional loop is typically composed of, digital loop filter (DLF), time-to-digital converter (TDC) and DCO [32]. In integer loop, also known as frequency-locked loop, the DCO coarse tuning is achieved by controlling the coarse (MSB, LSB) capacitor banks. It tunes the free running DCO frequency closest to target channel frequency which is an integer multiple of reference clock. It reduces the frequency locking time and DCO fine tuning range. It operates only once in the beginning when one of the forty BLE frequency channels is selected. When integer loop finishes, then the fractional loop starts its operation. The fractional loop accommodates the fractional part of frequency and aligns the phases of both DCO and reference clocks in the lock state. This loop is always active while ADPLL is operating. In proposed design, before fractional loop, DCO gain is estimated for compensating PVT variations and FSK direct modulation. Numerous techniques for integer loop design are discussed in literature [19], [20]. This paper explores a very simple, reliable adaptive design for all-digital frequency-locked loop in ADPLL applications for BLE transceiver. The binary algorithm is used in a dynamic adaptive way for evaluating binary bit values of MSB and LSB capacitor banks.

# A. ADAPTIVE FLL ALGORITHM

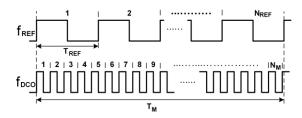

Fig. 2 explains the relationship between reference and DCO frequencies. The highly reliable fixed reference clock frequency  $f_{REF}$  is slower than that of DCO. Therefore, single reference clock cycle accommodates multiple DCO clocks. If the DCO clock cycles are measured for  $N_{REF}$  number of reference clock period  $T_{REF}$ , then the total duration,  $T_M$  is given in (1) as:

$$T_{M} = \frac{N_{REF}}{f_{REF}} = N_{REF} T_{REF} \tag{1}$$

If  $N_M$  DCO clock cycles are measured in  $T_M$  duration, then the DCO frequency is found in (2) as follows:

$$f_{DCO} = \frac{N_M}{T_M} = \frac{N_M}{N_{REF}} f_{REF} \tag{2}$$

Now, the target frequency  $f_{CH}$  for a particular BLE channel is already known, then the number of DCO clock cycles,  $N_C$  is calculated mathematically as follows in (3):

$$N_C = \frac{f_{CH}}{f_{REF}} N_{REF} \tag{3}$$

The DCO capacitor banks are tuned in such a way that the measured  $N_M$  and calculated  $N_C$  number of DCO clock cycles are same. When this condition  $(N_M \approx N_C)$  is achieved then the DCO frequency  $f_{DCO}$  is closest to the target channel frequency  $f_{CH}$ . In ADPLL design, this goal is achieved in the integer loop before the gain estimation and fine tuning and phase locking in fractional loop. Thus, the design of FFL is very critical in order to achieve an accurate target frequency in an ADPLL. In this paper, a simple, hardware friendly adaptive FLL design for integer loop is presented. For the evaluation of each bit of coarse capacitor bank, DCO frequency is measured for an adaptive number of reference clock cycles instead of fixed duration. The number of calculated DCO clock cycles are also adaptive with respect to the capacitor bit position. In the proposed design, the adaptive number of reference clock period,  $N_{REF}(n)$  is defined as follows in (4):

$$N_{REF}(n) = 2^{N-n} \tag{4}$$

Where, N is the total number of bits in the binary capacitor control word (CCW) for MSB and LSB capacitor banks. The n is current bit position which is being evaluated for DCO frequency measurement. Its range is  $0 \sim N-1$ . The  $N_{REF}(n)$  is the function of capacitor bank bit position and its value increases dynamically as n decrements from N-1 to 0. The total duration for DCO cycles count also becomes adaptive and is function of n, defined in (5) as follows:

$$T_M(n) = \frac{2^{N-n}}{f_{RFF}} \tag{5}$$

When,  $N_M$  is measured for  $T_M(n)$  interval for particular bit position n, then the DCO frequency is given by (6) as follows:

$$f_{DCO} = \frac{N_M}{2^{N-n}} f_{REF} \tag{6}$$

The calculated number of reference clocks is now the function of CCW bit position, n and selected frequency channel. It is also adaptive and changes dynamically as the frequency channel and bit position vary. The adaptive number of reference clock cycles,  $N_C(n, k)$  are given in (7) as follows:

$$N_{C}(n,k) = \frac{f_{CH}(k)}{f_{RFF}} 2^{N-n}$$

(7)

Where, k = 0, 1, 2, 3 ... 39 which corresponds to selected BLE frequency channels CH0~CH39. The simplified result of (7) is given as follows in (8):

$$N_{C}(n,k) = \frac{N_{FCW}(k)}{2^{n-\frac{N}{2}}}$$

(8)

The  $N_{FCW}(k)$  is the frequency control word as a function of k and is computed by (9) as follows:

$$N_{FCW}(k) = k + N_{CH_0}(\frac{M}{D} \times 10^{-6})$$

(9)

Here  $N_{CH0}$  is the base frequency magnitude of CH0, M is the DCO frequency multiplier factor and N is the DCO frequency division factor.

Since, the inductor size is very critical in LC-tank based DCO design therefore, for any specific application, the minimum frequency  $f_{MIN}$  is limited by the maximum inductance  $L_{MAX}$ . For lower frequencies, the inductor size is bigger which results in an increase in area, power consumption and cost. One technique for comparatively reducing inductor size is to design DCO with integer multiple of the required frequency and then divide the frequency with the same integer to get required frequency. In this way the inductor size is reduced. This technique also improves the DCO phase noise. If, M is this multiplying factor then the DCO is running with the frequency as given in (10):

$$f_{DCO} = M f_{TAR} \tag{10}$$

The DCO running frequency is measured by counting its clock cycles. The counter size is dependent on the frequency and mask time. The DCO frequency is divided by an integer division factor *D* to reduce the area and power consumption of the counter.

## **B. DCO GAIN ESTIMATION**

After FLL locking, the DCO gain estimation, single bit fine capacitor bank resolution, is determined before the fine tuning in integer loop. The gain estimation is essential for compensating PVT variations and calculating the deviation ratio before the start of direct modulation in BLE transceiver. It is calculated by counting the DCO clock cycles with setting the FINE capacitor back to its maximum and minimum values. The DCO gain,  $K_{DCO}$  is computes as follows by the (11):

$$K_{DCO} = \frac{N_{MAX} - N_{MIN}}{2^{N_{FINE}}} \tag{11}$$

Where,  $N_{MAX}$  and  $N_{MIN}$  are the maximum and minimum number of DCO clock cycles when the FINE capacitor bank is set to its minimum and maximum positions respectively and  $N_{FINE}$  is the total number of fine capacitor bank bits.

## C. LOW POWER DCO DESIGN

The oscillation condition [27] for low power CMOS cross coupled LC-tank DCO is written as follows:

$$g_{\scriptscriptstyle m} \ge \frac{1}{R_{\scriptscriptstyle P}} \tag{12}$$

Where,  $R_P$  and  $g_m$  are the equivalent parallel resistance of the passive section and the equivalent transconductance of active section respectively. The  $g_m$  of the NMOS transistors is added to  $g_m$  of the PMOS transistors constructively in the CMOS complementary structure. Therefore, compared to NMOS-only or PMOS-only architecture, the power consumption of cross-coupled structure is halved with the same current

consumption. In now a day's battery operated devices, the low power consumption and low supply voltage are highly desired. The MOS transistor operation in sub-threshold region is suitable for low power consumption and low supply voltage requirements. The gate to source voltage  $V_{GS}$  is less than the threshold value  $V_{TH}$  in sub-threshold region. The drain current,  $I_D$  in sub-threshold region is described as follows:

$$I_{D} = \mu_{0} C_{ox} \left(\frac{W}{L}\right) (m-1) U_{T}^{2} e^{\frac{(V_{GS} - V_{TH})}{mU_{T}}} (1 - e^{\frac{V_{DS}}{U_{T}}})$$

(13)

where  $U_T = KT/q$ , K, T, q,  $\mu_0$ , and  $C_{ox}$  are thermal voltage, Boltzman's constant, temperature, electron charge, surface mobility and gate-oxide capacitance respectively. The parameter m represents capacitive coupling between silicon surface and gate. In sub-threshold region, the transconductance is expressed as follows:

$$g_m = \frac{I_D}{mU_T} \tag{14}$$

By selecting larger inductances, the power consumption is minimized. The  $R_P$  is calculated as follows:

$$R_p = 2\pi f_0 L Q_L \tag{15}$$

Where,  $f_0$  is oscillation frequency, L is inductance value and  $Q_L$  is quality factor of inductor. From (12) and (15), the oscillation condition is expressed as follows:

$$g_m \ge \frac{1}{2\pi f_0 L Q_t} \tag{16}$$

Thus, minimum transconductance,  $g_{m,min}$  is as follows:

$$g_{m,\min} = \frac{1}{2\pi f_0 L Q_L} \tag{17}$$

According to (17), the oscillation condition is satisfied with larger inductance and smaller  $g_m$  in the sub threshold region. This results in less power consumption with lower supply voltage. The tail bias current is  $I_{bias} = 2I_D$  and its lower limit for sustainable oscillation is described as follows in (18):

$$I_{bias} = \frac{1}{\pi f_0 L Q_L(\frac{g_m}{I_D})}$$

(18)

For the given bias condition in (18), MOS transistors provide high transconductance when operating in the sub-threshold region. The transconductance efficiency  $(g_m/I_D)$  is maximum in the sub-threshold region while it is minimum in super-threshold region. The oscillation frequency  $f_0$  of LC-tank DCO is given by the following (19):

$$f_0 = \frac{1}{2\pi\sqrt{LC}}\tag{19}$$

FIGURE 3. All-digital FLL architecture.

Where, C and L are the effective capacitance and inductance respectively. This relation is re-written in more detail as follows in (20):

$$f = \frac{1}{2\pi\sqrt{L_F.(C_F + n\Delta C)}}; (n = 0, 1, \dots 2^N - 1)$$

(20)

Where  $L_F$  is the fixed inductance including the parasitic inductance and  $C_F$  is the fixed capacitance including the parasitic capacitance. The N is the total number of bits and  $\Delta C$  is the minimum capacitance.

From (20), the oscillation frequency of DCO is approximated as follows:

$$f_0 = f_{\text{MAY}} - n\Delta f \tag{21}$$

Where

$$f_{MAX} = \frac{1}{2\pi \sqrt{L_{E}C_{E}}}$$

and  $\Delta f = \pi \cdot \frac{\Delta C}{C_{E}} \cdot f_{MAX}$

By using (21), the inductance of the DCO LC-tank is computed as follows in (22):

$$L_F = \frac{2\Delta f}{f_{\text{MAY}}^3 \Delta C} \tag{22}$$

For the particular DCO application,  $f_{MAX}$  is defined to a fixed value and as a result fixed maximum inductance  $L_{MAX}$  is achieved. Hence,  $C_F$  defines an upper limit for  $L_{MAX}$ . According to (22), with smaller  $\Delta C$  value, fine frequency step

$\Delta f$  is achieved and it controls DCO quantization noise within entire system. If the  $\Delta C$  is divided into MSB, LSB and FINE capacitor banks, then (20) is given as follows in (23):

$$f = \frac{1}{2\pi\sqrt{L_F.(C_F + n_{MSB}\Delta C_{MSB} + n_{LSB}\Delta C_{LSB} + n_{FINE}\Delta C_{FINE})}}$$

(23)

Where;

$$\begin{split} &n_{MSB}\Delta C_{MSB} \simeq \Delta C_{TOT} \\ &n_{LSB}\Delta C_{LSB} \simeq 2\Delta C_{MSB}; \Delta C_{LSB} = 0.5\,fF \\ &n_{FINE}\Delta C_{FINE} \simeq 4\Delta C_{LSB}; \Delta f = 2.4kHz \\ &\Delta C_{FINE} \simeq 16aF \end{split}$$

The  $\Delta C_{MSB}$ ,  $\Delta C_{LSB}$  and  $\Delta C_{FINE}$  are the unit capacitances for MSB, LSB and FINE capacitor banks respectively for attaining desired frequency resolution.

## III. ADAPTIVE ALL-DIGITAL FLL ARCHITECTURE

The detailed architecture of the proposed all-digital FLL is depicted in Fig. 3. The major building blocks includes, all-digital adaptive FLL controller (ADAFLLC), LC-tank DCO and adaptive LDO (ALDO). The detail of each block is discussed in next sub-sections.

## A. ALL-DIGITAL ADAPTIVE FLL CONTROLLER

The synthesizable digital circuit design methodologies using behavioral description languages is of great interest due to reusability, simplicity and easy scalability of the circuit as

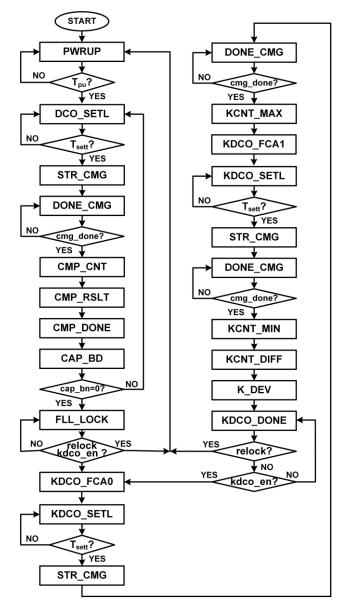

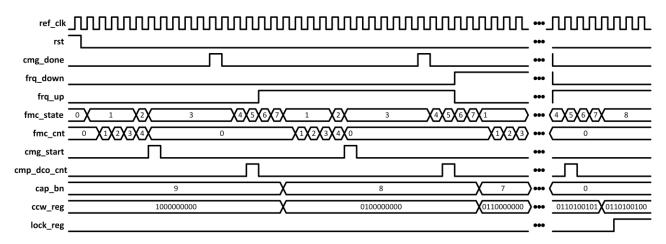

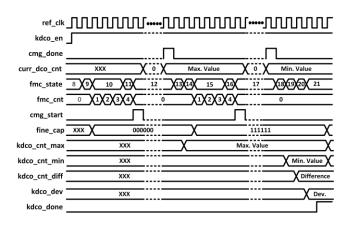

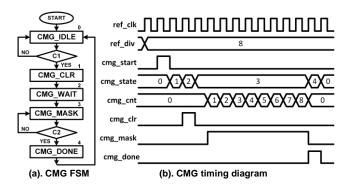

compared to custom design [21]. Therefore, proposed ADAFLLC is designed with fully synthesizable digital controller and it tunes coarse (MSB, LSB) capacitor banks for target frequency and also performs gain estimation. The FLL main controller (FMC) ensures the operation of each block and generates the exact CCW for selected frequency channel in various modes. After, integer frequency is locked, the DCO gain estimation is computed. The FMC flow diagram is depicted in Fig. 4 while Fig. 5 explains its timing diagram for frequency lock operation. Fig. 6 summarizes the timing diagram for DCO gain estimation. This controller is designed as finite state machine (FSM) control unit and related datapath. On power up, FMC is in PWRUP state and it stays for configurable duration. This state facilitates chip soft start operation, eliminates proposed design's contribution to inrush current and waits for the settling of other analog and digital blocks within the chip. All registers are assigned their default values in reset state. The capacitor control word register ccw\_reg is set to its central value 10000\_00000B. After power up, the controller moves to DCO\_SETL state. The DCO stables its frequency in DCO\_SETL state whenever CCW changes. The FMC enables counter mask generator (CMG) in STR\_CMG state and waits for DCO clock cycle counting against current capacitor bit in DONE\_SMG state. The CMG, with FSM flow chart and its timing diagram is elaborated in Fig. 7, controls DCO clock counter (DCC) and enables it for specific number of reference clock cycles. It generates the counter mask during which DCC counts DCO clock cycles to measure current frequency. The reference divider generator (RDG) generates reference clock cycle numbers according to (4) as function of current bit position and selected mode. This mask duration, defined in (5) is the function of reference clock frequency, FLL mode and MSB/LSB capacitor bit position, n for which mask is generated. When DCO frequency measurement finishes, the FMC directs DCO frequency detector (DFD) to determine either the oscillator is running faster or slower than the required frequency in CMP CNT state. In state CMP\_RSLT, the DFD compares measured DCO clock cycles curr\_dco\_cnt with the calculated cal\_dco\_cnt,

FIGURE 4. FMC finite state machine.

FIGURE 5. FMC timing diagram for frequency lock loop.

FIGURE 6. FMC timing diagram for gain estimation.

computed by clock count generator (CCG) according to (8) as function of unique frequency control word from frequency control word generator (FCWG) for each BLE channel. The comparison result is available in CMP DONE state for taking decision about current CCW bit. This bit decision is taken in CAP BD state. If the DCO is running faster than the required frequency, then it needs to be slowed down by increasing capacitor bank capacitance. For this, DFD asserts freq\_down high while keeping freq\_up low. In this case, the current CCW bit remains high. The FMC turns on the next least significant bit high and jumps back to DCO SETL state for computing the new frequency of DCO after changing capacitance. If the DCO is running slow than the required frequency, the DFD pulls the freq\_up to high and grounds the freq\_down signal. In this case, the capacitance needs to decrease in order to increase frequency. The current CCW bit changes from one to zero and next least significant bit is set to one. This process continues till the least significant bit is checked. In CAP\_BD state, if all CCW bits are evaluated, then the current DCO frequency becomes approximately equal to the target frequency with minimum fractional error. The CCW is fixed to evaluated value and it is locked in FLL LOCK state. After FLL lock, FMC determines DCO gain estimation according to (11). The controller sets all the fine capacitor bank bits fine\_cap to zero in KDCO\_FCA0 state and waits for settling for configurable duration in KDCO SETL state. The CMG is started in STR CMG and waits for finishing the mask duration for

FIGURE 7. CMG finite state machine and timing diagram.

measuring the DCO frequency in DONE\_CMG state. The curr\_dco\_cnt gives the maximum value which is saved in kdco\_cnt\_max register in KCNT\_MAX state. Similarly, the fine capacitor bank bits are set to high and against this, the minimum counter value, measured as result of same fixed number of reference clock cycles are registered in kdco\_cnt\_min in KCNT\_MIN state. The difference kdco\_cnt\_diff of both count values are computed in KCNT\_DIFF state and final deviation kdco\_dev is evaluated in K\_DEV state. The DCO gain estimation process is complete and controller announces this in KDCO\_DONE state by asserting the kdco\_done signal high. The controller remains in this state until there is request of computing DCO gain estimation again or repeating the FLL operation.

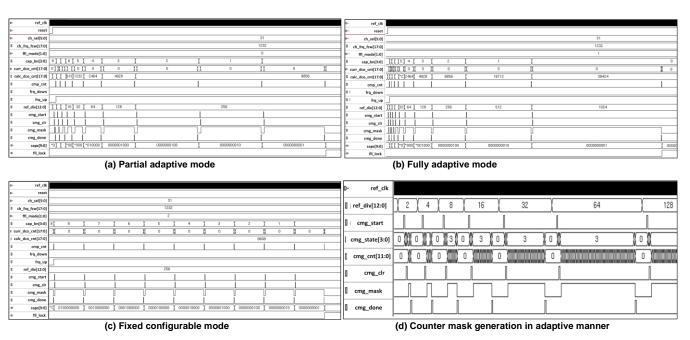

In the presented FLL design, four configurable operating modes are proposed. These modes control the masking duration for counting DCO clock cycles in various methods. The fully adaptive mode (FAM) is the default mode, in which the counter mask is fully adaptive from MSB to LSB of the capacitor banks. This is the most accurate mode in terms of frequency measurement at the cost of comparatively more locking time. In partial adaptive mode (PAM), the counter mask is adaptive for selectable initial MBS and then become fixed for remaining bits to reduce the lock time. One of the configurable mask is selected and remains fixed during all iterations for capacitor bits in the fixed configurable mode (FCM). In this mode, the locking time depends in the selected mask. In external manual mode (EMM), the capacitor bits and locking signal are directly controlled from external controller for manual debugging and analysis purpose.

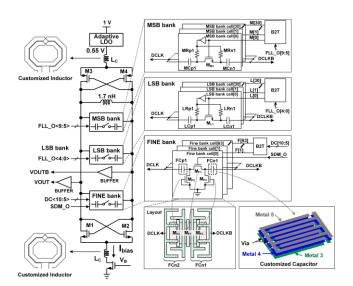

#### B. DIGITALLY CONTROLLED OSCILLATOR (DCO)

The LC-tank DCO is key building block in ADPLL and it consumes most of system power for generating local frequency [1], [25], [31], [35], [36]. Therefore, ultra-low power and ultra-low voltage DCO design significantly reduces system power consumption [37], [38]. The DCO performs digital-to-frequency conversion [32]. The constant current DCO configuration and simplified circuit diagram with MSB, LSB and FINE capacitor banks is shown in Fig. 8 [27]. Since the DCO power consumption is dominant factor in ADPLL in open loop operation, therefore DCO is designed with low power techniques. For minimizing current consumption and relaxing reliability problems, DCO supply is 0.55 V and it is relatively lower than other building blocks. The DCO is designed with ULP process and threshold voltage,  $V_{TH}$  is very small  $(0.18 \text{ V} \sim 0.2 \text{ V})$  for this process. The overdrive voltage is 0.1 V. The two transistor can get enough voltage form 0.55 V power supply. The 4-stack transistor (negative gm transistor) can get needed overdrive voltage from 0.55 V power supply. The sigma-delta modulator for dithering and binary to thermometer encoder (B2T) DCO digital sub-blocks can operate at 0.55 V supply. The DCO operates and have oscillations with supply voltage from 0.55 V to 1 V. The power consumption will increase if the DCO supply is

FIGURE 8. DCO design.

increased from 0.55 V to 1V. Therefore, the lowest possible supply voltage of 0.55 V is used for minimum power consumption. The 1.2 V devices are used for the presented DCO and transistors reliability is assured for 1.32 V as maximum voltage. Although, peak voltage exceeds than oscillator VDD, it does not increase more than 1.2 V as analyzed from simulation results. Since a larger inductor reduces DCO power consumption, therefore, the main inductor is maximized while the parasitic capacitance is minimized for desired frequency range. The DCO phase noise depends on the frequency resolution, which is limited by the minimum switchable capacitance. For DCO design flexibility and frequency step linearity, the coarse and fine capacitor banks are designed with unit weighted capacitor rather than binary weighted configuration. By optimizing capacitor redundancies, parasitic capacitance is reduced by utilizing flexible number of capacitors in unit weighted structure in comparison with a binary weighted structure. For attaining high linearity and small switchable capacitance, a customized lateral metal capacitor is designed and fabricated, as shown in Fig. 8. Its capacitance is calculated from RC extraction which has 16 aF value approximately. The configurable MSB and LSB capacitor banks are designed with a variable bias switched capacitor. To improve LC- tank Qfactor, metal-insulator-metal (MIM) and metal-oxide-metal (MOM) capacitors are commonly employed instead of MOS capacitors for MSB and LSB capacitor banks. The MOM capacitors are used for designing low cost DCO with improved Q-factor. For minimizing area and increasing capacitor density, these capacitors are stacked from Metal 2 to Metal 5. Because the LSB capacitor bank requires minimum capacitance in the process design kit (PDK) therefore these MOM capacitors are stacked from Metal 3 to Metal 5. The unit capacitor cell is composed of a switch, two capacitors and two blocking resistors as elaborated in Fig. 8. Conventionally, the switch source bias voltage is fixed to zero. However, in case of DCO large swing, switch is not turned off completely in OFF-mode. This causes phase noise degeneration. To overcome this problem, two inverters are utilized as control logic for providing variable biasing. In ON-mode, the switch transistor source voltage is biased at zero while gate voltage is VDD (1V). On the other hand, in OFF-mode, gate and source voltages of switch are biased at zero and about LDO<sub>OUT</sub> (0.55V) respectively to ensure complete switch turn off. An ultra-wide width aluminum (Al) pad metal pattern is incorporated to eliminate the parasitic resistance and inductance due to metal routings. This only creates additional capacitance between Al pattern and capacitor banks. There is no stray parasitic capacitance problem due to large distance of about 8.8 µm between Al pattern and substrate. Aluminum pad metal has sufficiently large thickness and no width limitation. All parasitic inductors are tied in parallel with ultra-wide width Al pad metal and via. In this way, parasitic inductors are eliminated effectively. As a result, the DCO is parasitic inductance free and ensures linear frequency steps. As a result, frequency steps are closer to that of measurement and accurate oscillation frequency is achieved without additional cost for Al pad layer. For dithering, one out of 64 cells of FINE capacitor bank is controlled by the first order sigma-delta modulator (SDM). Therefore, SDM dithering effective frequency resolution is 1/16 of the 1-bit frequency resolution of the FINE capacitor bank. In DCO design, there is trade-off between oscillation frequency range and power consumption. The two Lc inductors at top and bottom of DCO are customized design. The inductance of each of these inductors is 3 nH. Each inductor has very small resistance and there is very small voltage drop improving PN by 6 dB at 1-MHz offset. The purpose of these inductors is to improve the phase noise of the DCO. Firstly, two inductors are designed based on EMX simulation and then its quality factor and inductance values are calculated as 15 and 3 nH respectively. The negative gm-cell placement also affects DCO power consumption and frequency range. If all transistor switches are off, the DCO exhibits large parasitic inductance, reduces frequency and decreases current consumption when a negative  $g_m$  cell is placed at capacitor banks end side. Similarly, if a negative  $g_m$  cell is positioned at inductor end side then the negative  $g_m$  cell Q-factor degrades and DCO power dissipation increases. Therefore, for designing low power DCO, the negative  $g_m$  cell is located at capacitor banks end side in the proposed FLL.

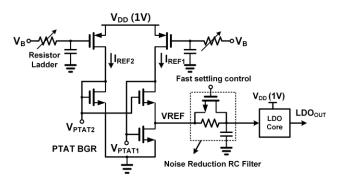

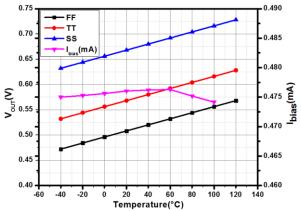

# C. ADAPTIVE LDO

The minimum oscillation and power dissipation of DCO changes with PVT variations. When constant voltage source is used, the DCO draws more current at corner cases due to decrease in  $g_m$ . To provide constant current to DCO, an adaptive LDO [27], depicted in Fig. 9 is integrated as DCO driving voltage source. The LDO output voltage automatically changes with PVT variations to keep  $g_m$  constant. The proportional to absolute temperature (PTAT)

FIGURE 9. Adaptive LDO design.

bandgap reference (BGR) compensates temperature variations and LDO function regulates voltage variation. With PTAT BGR, ALDO ensures constant voltage and current across DCO at corner cases. At corner conditions, constant current keeps DCO  $g_m$  constant and reduces DCO power consumption significantly. With ALDO, around 50% power consumption is reduced at the corners.

#### IV. EXPERIMENTAL RESULTS

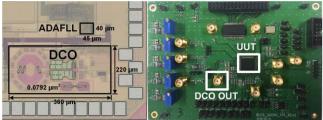

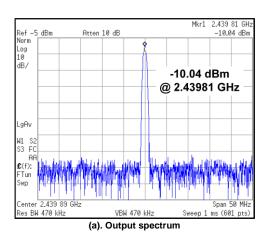

The proposed adaptive all-digital FLL is fabricated by using 55 nm 1P6M TSMC CMOS technology. It is part of ADPLL in BLE transceiver for IoT applications. The power supplies for fully synthesizable FLL and DCO are 1 V and 0.55 V respectively. Fig. 10(a) shows the chip microphotograph with 45  $\mu m \times 40~\mu m$  and 360  $\mu m \times 220~\mu m$  area of ADAFLLC and DCO respectively with total 0.081 mm² area. Fig. 10(b) shows the testing board with fabricated BLE chip for measuring proposed design. Fig. 11 shows lab

(a). Microphotograph

(b). Measurement board with UUT

FIGURE 10. Chip microphotograph and measurement board.

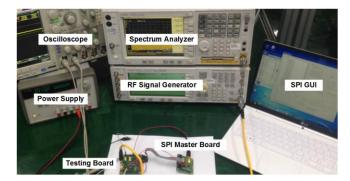

FIGURE 11. Measurement lab setup.

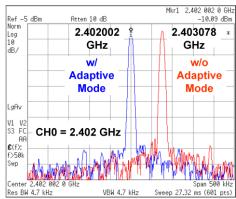

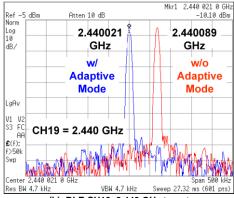

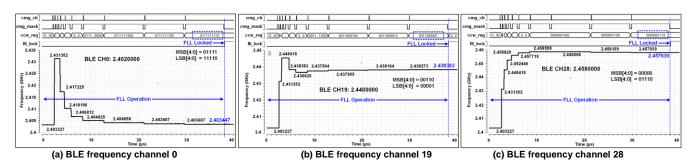

(a). BLE CH0, 2.402 GHz target

(b). BLE CH19, 2.440 GHz target

(c). BLE CH39, 2.480 GHz target

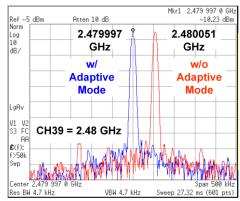

FIGURE 12. All digital FLL measurement results.

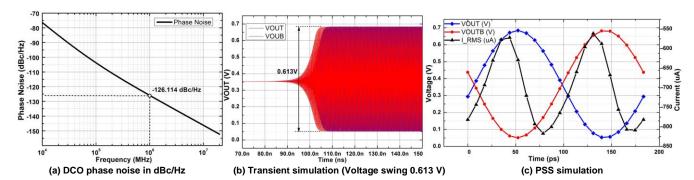

FIGURE 13. DCO output spectrum and phase noise measurement

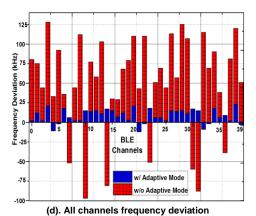

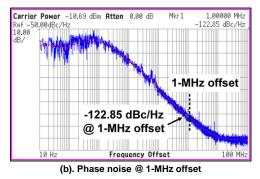

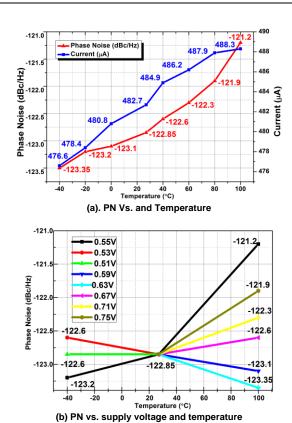

experimental environment for measuring the performance of FLL and DCO for which spectrum analyzer, signal generator, oscilloscope and power supply are used. Fig. 12 shows the measurement results for integer ADAFLLC operations. The measurement results show that the locked frequency for selected channel is more near to the target frequency with proposed adaptive design. In Fig. 12(a), the BLE CH0 target frequency is 2.402 GHz. The frequency deviation from target one is 2 kHz only with adaptive mode while it is 1.078 MHz without adaptive mode. Similarly, for CH19 and CH39, the frequency deviation is much less with proposed FLL in adaptive mode as shown in Fig. 12(b) and Fig. 12(c) respectively. The measurement results for frequency deviation of all forty BLE channels with and without adaptive mode are elaborated in Fig. 12(d). The measurement results prove that the proposed ADAFLLC design is highly effective and lock the integer loop with frequency which is much closer to the target frequency. The frequency deviation is greater in case of without adaptive mode. Fig. 13(a) and (b) show the measured output spectrum and phase noise of DCO respectively. At 1-MHz offset, the measured PN is -122.85 dBc/Hz. The DCO measured performance of PN versus supply voltages and current consumption are plotted in Fig. 14. As shown in Fig. 14, phase noise value, a DCO key characteristic is good compared with that of supply voltage and current consumption. The measurement results for coarse (MSB, LSB), FINE capacitor banks and SDM dithering frequency

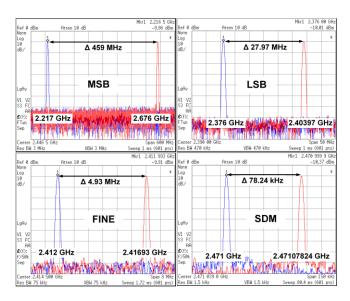

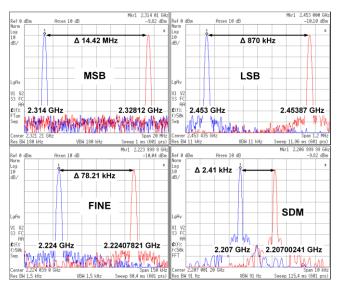

FIGURE 14. DCO measurement results with different conditions.

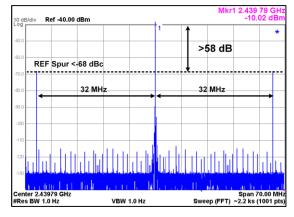

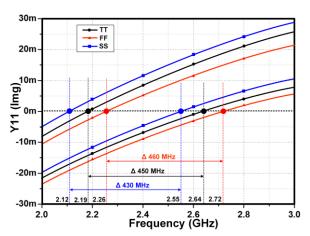

tuning range are elaborated in Fig. 15. The MSB, LSB, FINE capacitor banks and dithering SDM frequency step are 459 MHz, 27.97 MHz, 4.93 MHz, and 78.24 kHz, respectively. The measured tuning range for DCO is 459 MHz from 2.217 GHz to 2.676 GHz and it is depicted in Fig. 15 (a). The MSB, LSB, FINE capacitor banks and SDM dithering measured 1bit resolutions are 14.42 MHz, 870 kHz, 78.21 kHz and 2.41 kHz respectively as depicted in Fig. 16. Table I summarizes the performance of fully synthesizable FLL. Its power consumption is 103.32 µW for its full operation. For its implementation in chip, it requires only 1.233 K gates with 1800 μm<sup>2</sup> chip area. The lock time ranges 3.7~6487 μs and it depends on the selected mode and configured parameters. The DCO performance and comparison with existing designs is listed in Table II. It needs 0.264 mW power for its full operation. It occupies a very small chip area of 0.0792 mm<sup>2</sup> when compared with prior works. The PN is -122.85 dBc/Hz. The FOM and total figure of merit (FOM<sub>T</sub>) are 196.38 dBc/Hz and 208.19 dBc/Hz respectively confirming its good performance for low voltage and low power applications including BLE. The FOM and FOM<sub>T</sub> are evaluated with (24) and (25) respectively [33], [34].

$$FOM = |PN| + 20\log_{10}(\frac{f_0}{\Delta f}) - 10\log_{10}(\frac{P_{DC}}{1wW})$$

(24)

FIGURE 15. Frequency step measurement for MSB, LSB, FINE and SDM.

FIGURE 16. 1-bit resolution measurement for MSB, LSB, FINE and SDM.

$$FOM_T = |PN| + 20\log_{10}((\frac{f_0}{\Delta f})(\frac{\%FTR}{10})) - 10\log_{10}(\frac{P_{DC}}{1wW})$$

(25)

The FLL performance comparison with the exiting counter based topologies is summarized in Table III [22], [25], [26]. Most of previous integer FLL work such as in [22] and [25] used fixed number of clock cycles for each capacitor bank bit evaluation. In contrast, for locking DCO frequency closest to target channel, proposed FLL algorithm adaptively controls capacitor banks with binary algorithm. With decrease in frequency resolution, DCO clock counts for each capacitor bank bit evaluation dynamically increases with the proposed technique for accurate frequency tracking. Additionally, the configurable digital DCO gain estimation is incorporated for compensating PVT variations and finding the BLE frequency deviation. Finally, in the presented work,

TABLE I ADAFLL PERFORMANCE SUMMARY

| Parameter              | Value       |

|------------------------|-------------|

| CMOS technology        | 55 nm       |

| Occupied Area          | 1800 μm²    |

| Gate count             | 1.233 K     |

| Supply voltage         | 1 V         |

| Current consumption    | 103.32 μΑ   |

| Power consumption      | 103.32 μW   |

| <sup>1</sup> Lock time | 3.7~6487 μs |

<sup>&</sup>lt;sup>1</sup>Lock time depends on mode and configured parameters

TABLE II DCO PERFORMANCE SUMMARY AND COMPARISON

| Deo i en ormane benimari and com anson |          |           |              |              |  |

|----------------------------------------|----------|-----------|--------------|--------------|--|

| Parameter                              | Ref. [1] | Ref. [27] | Ref.<br>[31] | This<br>Work |  |

| CMOS Process (nm)                      | 40       | 55        | 180          | 55           |  |

| Supply Voltage (V)                     | 1        | 0.55      | 1.8          | 0.55         |  |

| Oscillation Frequency (GHz)            | 2.44     | 2.44      | 3.2          | 2.44         |  |

| Resolution (kHz)                       | 40       | 78.13     | 20           | 72           |  |

| Dithering Resolution (kHz)             | -        | 2.44      | -            | 4.8          |  |

| Frequency Tuning<br>Range (GHz)        | 2.1~2.7  | 2.2~2.7   | 2.8~3.2      | 2.1~3.05     |  |

| PN @ 1-MHz Offset<br>(dBc/Hz)          | -115.53  | -119.05   | -114.42      | -122.85      |  |

| $P_{DC}$ (mW)                          | 0.33     | 0.260     | 3.8          | 0.264        |  |

| Area (mm²)                             | 0.135    | 0.13      | 0.35         | 0.0792       |  |

| FOM (dBc/Hz)                           | 189.16   | 193.42    | 179.32       | 196.38       |  |

| FOM <sub>T</sub> (dBc/Hz)              | 196.98   | 199.12    | 181.82       | 208.19       |  |

|                                        |          |           |              |              |  |

TABLE III FLL Performance Comparison

| I LE I EN ORMANCE COM ANSON |         |         |      |          |  |  |

|-----------------------------|---------|---------|------|----------|--|--|

| Parameter                   | Ref.    | Ref.    | Ref. | This     |  |  |

|                             | [22]    | [25]    | [26] | Work     |  |  |

| CMOS Process                | 180     | 90      | 55   | 55       |  |  |

| FLL Topology                | CNT     | CNT     | CNT  | CNT      |  |  |

| Oscillator Type             | Ring    | SRO     | DCO  | DCO      |  |  |

| Frequency Range (GHz)       | 0.2539  | 2.36~2. | 2.44 | 2.1~3.05 |  |  |

|                             | ~1.367  | 5       |      |          |  |  |

| Reference Clock (MHz)       | 19.53   | 24      | 32   | 32       |  |  |

| Lock Time (µs)              | 2.92 µs | 20.63   | 37   | 3.7~6487 |  |  |

| Gain Estimation             | No      | No      | Yes  | Yes      |  |  |

| Adaptive Algorithm          | No      | No      | No   | Yes      |  |  |

| Configurable                | No      | No      | No   | Yes      |  |  |

| Multi-modes                 | No      | No      | No   | Yes      |  |  |

FIGURE 17. Measured reference spur in fractional mode

FIGURE 18. Adaptive LDO measurement result and corner simulation.

four configurable operating modes are proposed which control the masking duration for counting DCO clock cycles in various methods. The measured reference super for the fractional mode is less than -68 dBc, as depicted in Fig. 17. The ADLDO measurement and corner simulation results of is plotted in Fig. 18. The  $V_{OUT}$  increases with the increase in temperature. Without ADLDO, when constant voltage source is used, DCO draws more current due to the increase in  $g_m$ . With ADLDO at the corner conditions, this biasing current remains 50% for powering the oscillator. For same  $g_m$  with process variation, FF corner requires lower  $V_{OUT}$  than TT and SS corner requires less  $V_{OUT}$  than TT. With BGR constant current, diode connected MOS determines suitable

reference voltages. The MOS transistors threshold voltage changes due to process variation and as a result the reference voltage also changes. The  $V_{OUT}$  varies due to trimmed reference voltage and DCO has the same  $g_m$ , consumes constant current and dissipates similar power.

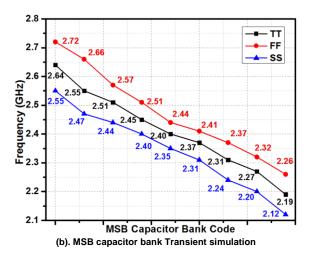

The Fig. 19 shows co-simulation for presented integer loop for BLE channels 0, 19 and 28. Fig. 19(a) shows the simulation result for BLE CH0 with 2.402 GHz target frequency. The DCO is tuned to 2.403447 GHz after FLL locking with the deviation of 1.447 MHz. Fig. 19(b) and Fig. 19 (c) show the simulations for channels 19 and 28 in which the locked frequency values are 2.438383 GHz and 2.457939 GHz with 1.617 MHz and 61 kHz frequency deviations respectively. Fig. 20 shows DCO post-payout simulation with 0.55 V power supply and 4.88 GHz oscillation frequency. The phase noise analysis is shown in Fig. 20(a). At 1-MHz offset from the operating frequency, the phase noise is -126.114 dBc/Hz. Fig. 20(b) shows the transient simulation DCO output in which maximum voltage swing is 0.613 V. The output of DCO obtained from periodic steadystate (PSS) analysis is shown in Fig. 20(c). The RMS current consumption of proposed DCO is around 463 µA. Fig. 21 shows the simulated frequency tuning range curves for the DCO. Fig 21 (a) shows DCO frequency tuning range curves based on SP simulation results. For finding frequency tuning range, the SP simulation is run to calculate the imaginary part of admittance (Y11) of 50 Ohm antenna port connected at DCO output. The minimum and maximum frequencies are 2.19 GHz and 2.64 GHz at Y11 zero crossing with tuning

FIGURE 19. All digital FLL settling behavior for selected channels.

FIGURE 20. DCO simulation analysis.

(a). SP Simulation results for tuning range curves

FIGURE 21. DCO frequency tuning range simulation results.

range of 450 MHz when capacitor codes are all high and all low respectively for TT corner case as shown in Fig. 21 (a). The transient simulation of MSB capacitor bank change based DCO frequency tuning range is shown in Fig. 21 (b). Since, MSB capacitor bank is for coarse tuning and it controls main capacitance, therefore its code is changed from minimum value to its maximum value to get the upper and lower DCO frequency limits respectively. With TT corner case, the transient simulation based DCO tuning range is 450 MHz as shown in Fig. 21(b). The Fig. 22 summarizes ADFLL simulation results for different proposed modes. This is post place and route (P&R) level open loop simulation of ADAFLLC digital part without the DCO in Synopsys® VCS® tool. Fig. 22 (a) shows the PAM simulation in which the *cmg mask* is adaptive from *cap bn* 9 to 2 and then become 256 as fixed for remaining bit positions. The CCG also generates cal dco cnt accordingly. Fig. 22(b) shows the fully adaptive mode simulation results. The ref div, calc dco cnt and cmg mask adaptively change as cap bn sweeps from MSB to LSB for DCO free running frequency tuning. The fixed configurable mode simulation is elaborated in Fig. 22(c) in which the one of the pre-defined fixed counter mask is generated for all cap bn values against any selected channel. The detailed simulation result for CMG is shown in Fig. 22(d). The adaptive mask generation is elaborated in which the mask time increases exponentially. The counter mask is configurable and adaptive with respect to cap bn. The cmg start is asserted high from FMC which initiates mask generation process. After receiving cmg start signal, CMG first clears the *cmg* cnt and then generates the mask for configured number of clock cycles according to the algorithm.

FIGURE 22. All digital FLL simulation results for different proposed operating modes and CMG simulation.

#### V. CONCLUSION

An ultra-low power, adaptive all-digital FLL with gain estimation and constant current DCO for BLE transceiver is presented in this paper. The binary algorithm adaptively controls capacitor banks for locking DCO frequency closest to the target channel. For accurate frequency tracking and tuning, DCO clock counts automatically increase for evaluating each bit of capacitor bank. For compensating PVT variations and finding the BLE frequency deviation, the configurable digital DCO gain estimation is incorporated. The low power constant current DCO operates in subthreshold region and its power consumption is minimized by  $g_m/I_D$  methodology optimization, constant current source for limiting current in the oscillator core through adaptive LDO and lowering the supply voltage. The ADAFLLC is fully synthesizable, occupies 1800 µm<sup>2</sup> area, utilizes 1.233 K gates, draws 103.32 uA RMS current from 1 V voltage source and dissipates 103.32 µW power. The DCO current consumption is 480 µA from 0.55 V supply at central frequency and has 4.8 kHz frequency resolution. At 1-MHz offset frequency from 2.44 GHz carrier frequency, DCO PN, FoM and FoM<sub>T</sub> are -122.85 dBc/Hz, 196.38 dbc/Hz and 208.19 dBc/Hz, respectively. The presented design is integrated in ADPLL. It is fabricated by using 55 nm 1P6M TSMC CMOS technology.

## **REFERENCES**

- [1] V. K. Chillara et al., "An 860 μW 2.1-to-2.7GHz All-Digital PLLBased Frequency Modulator with a DTC-Assisted Snapshot TDC for WPAN (Bluetooth Smart and ZigBee) Applications", IEEE International Solid-State Circuits Conference, pp. 172–173, Feb. 2014.

- [2] O. Omeni, A. C. W. Wong, A. J. Burdett, and C. Toumazou, "Energy efficient medium access protocol for wireless medical body area sensor networks," *IEEE Trans. Biomed. Circuits Syst.*, vol. 2, no. 4, pp. 251–259, Dec. 2008.

- [3] Y. Zhao, C. Lian, X. Zhang, X. Sha, G. Shi and W. J. Li, "Wireless IoT Motion-Recognition Rings and a Paper Keyboard", *IEEE Access*, vol. 7, pp. 44514-44524, April 2019.

- [4] M. Magno, G. A. Salvatore, P. Jokic and L. Benini, "Self-Sustainable Smart Ring for Long-Term Monitoring of Blood Oxygenation", *IEEE Access*, vol. 7, pp. 115400-115408, July 2019.

- [5] G. Shan and B. Roh, "Advertisement Interval to Minimize Discovery Time of Whole BLE Advertisers", *IEEE Access*, vol. 6, pp. 17817-17825, March 2018.

- [6] B. Luo, F. Xiang, Z. Sun and Y. Yao, "BLE Neighbor Discovery Parameter Configuration for IoT Applications", *IEEE Access*, vol. 7, pp. 54097-54105, April 2019.

- [7] F. Ye, R. Chen, G. Guo, X. Peng, Z. Liu and L. Huang, "A Low-Cost Single-Anchor Solution for Indoor Positioning Using BLE and Inertial Sensor Data", *IEEE Access*, vol. 7, pp. 162439-162453, Nov. 2019.

- [8] Bluetooth. (Dec. 2014). Specification of the Bluetooth System v4.2. [Online]. Available: https://www.Bluetooth.org

- [9] J. Mo, Z. Deng, B. Jia, H. Jiang and X. Bian, "A Novel FLL-Assisted PLL With Fuzzy Control for TC-OFDM Carrier Signal Tracking", *IEEE Access*, vol. 6, pp. 52447-52459, Sep. 2018.

- [10] Z. Yang, Y. Chen, S. Yang, P. Mak and R. P. Martins, "A 10.6-mW 26.4-GHz Dual-Loop Type-II Phase-Locked Loop Using Dynamic Frequency Detector and Phase Detector", *IEEE Access*, vol. 8, pp. 2222-2232, Dec. 2020.

- [11] G. D'Amato, G. Avitabile, G. Coviello and C. Talarico, "DDS-PLL Phase Shifter Architectures for Phased Arrays: Theory and Techniques", *IEEE Access*, vol. 7, pp. 19461-19470, Jan. 2019.

[12] H. Xue, Y. Cheng and M. Ruan, "A Hybrid Pre-loop/Post-loop Filtering Strategy Based Type-1 PLL for Synchronization Under Distorted Grid Conditions", 2019 IEEE Power & Energy Society General Meeting (PESGM), pp. 1-5, Jan. 2019.

**IEEE** Access

- [13] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero and J. Doval-Gandoy, "A Quasi-Type-1 Phase-Locked Loop Structure", *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6264-6270, Dec. 2014

- [14] A. Sharkia, S. Aniruddhan, S. Shekhar and S. Mirabbasi, "A high-performance, yet simple to design, digital-friendly type-I PLL", *IEEE Custom Integrated Circuits Conference (CICC)*, pp. 1-4, Sep. 2015.

- [15] J. Moon, K. Choi and W. Choi, "A 0.4-V, 90 350-MHz PLL With an Active Loop-Filter Charge Pump", IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 61, no. 5, pp. 319-323, May 2014.

- [16] L. C. Liu and B. H. Li, "Fast locking scheme for PLL frequency synthesizer", *Electronics Letters*, vol. 40, no. 15, pp. 918-920, July 2004.

- [17] W. Chiu, Y. Huang and T. Lin, "A Dynamic Phase Error Compensation Technique for Fast-Locking Phase-Locked Loops", IEEE J. Solid-State Circuits, vol. 45, no. 6, pp. 1137-1149, June 2010.

- [18] D.-S. Kim, H. Song, T. Kim, S. Kim, and D.-K. Jeong, "A 0.3–1.4 GHz all-digital fractional-N PLL with adaptive loop gain controller," *IEEE J. Solid State Circuits*, vol. 45, no. 11, pp. 2300–2311, Nov. 2010

- [19] B. Liu et al., "A 0.4-ps-Jitter -52-dBc-Spur Synthesizable Injection-Locked PLL With Self-Clocked Nonoverlap Update and Slope-Balanced Subsampling BBPD", IEEE Solid-State Circuits Letters, vol. 2, no. 1, pp. 5-8, Jan. 2019.

- [20] W. Deng et al., "A Fully Synthesizable All-Digital PLL With Interpolative Phase Coupled Oscillator, Current-Output DAC, and Fine-Resolution Digital Varactor Using Gated Edge Injection Technique", *IEEE J. Solid State Circuits*, vol. 50, no. 1, pp. 68-80, Jan. 2015.

- [21] B. S. Kirei, C. Farcas, R. Groza and M. D. Topa, "An all-digital frequency locked loop and its linearized S-domain model", *International Symposium ELMAR*, pp. 91-94, Sep. 2017.

- [22] J. Lin and C. Yang, "A Fast-Locking All-Digital Phase-Locked Loop With Dynamic Loop Bandwidth Adjustment", *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 62, no. 10, pp. 2411-2422, Oct. 2015.

- [23] S.-Y. Yang, W.-Z. Chen, and T.-Y. Lu, "A 7.1 mW, 10 GHz all digital frequency synthesizer with dynamically reconfigured digital loop filter in 90 nm CMOS technology", *IEEE J. Solid State Circuits*, vol. 45, no. 3, pp. 578–586, Mar. 2010.

- [24] C.-C. Hung, I.-F. Chen, and S.-I. Liu, "A 1.25 GHz fast-locked all-digital phase-locked loop with supply noise suppression", *IEEE VLSI-DAT*, pp. 237–240, Apr. 2010.

- [25] S. J. Kim, D. Lee, K. Lee and S. Lee, 'A 2.4-GHz Super-Regenerative Transceiver With Selectivity-Improving Dual Q-Enhancement Architecture and 102μW All-Digital FLL", *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 9, pp. 3287-3298, Sept. 2017.

- [26] S. Oh et al., "A 3.9 mW Bluetooth Low-Energy Transmitter Using All-Digital PLL-Based Direct FSK Modulation in 55 nm CMOS", *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 9, pp. 3037-3048, Sept. 2018.

- [27] H. Abbasizadeh et al., "260-μW DCO with Constant Current over PVT Variations Using FLL and Adjustable LDO", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 65, no. 6, pp. 739-743, June 2018.

- [28] H. Guo, Y. Chen, P. Mak and R. P. Martins, "A 0.083-mm<sup>2</sup> 25.2-to-29.5 GHz Multi-LC-Tank Class-F234 VCO With a 189.6-dBc/Hz FOM", *IEEE Solid-State Circuits Letters*, vol. 1, no. 4, pp. 86-89, April 2018.

- [29] H. Guo, Y. Chen, P. Mak and R. P. Martins, "A 0.08mm<sup>2</sup> 25.5-to-29.9GHz Multi-Resonant-RLCM-Tank VCO Using a Single-Turn Multi-Tap Inductor and CM-Only Capacitors Achieving 191.6dBc/Hz FoM and 130kHz 1/f3 PN Corner", *IEEE International Solid-State Circuits Conference*, pp. 410-412, Feb. 2019.

- [30] R. B. Staszewski, D. Leipold, Chih-Ming Hung and P. T. Balsara, "A first digitally-controlled oscillator in a deep-submicron CMOS process for multi-GHz wireless applications", *IEEE Radio*

- Frequency Integrated Circuits (RFIC) Symposium, pp. 81-84, June 2003.

- [31] C-Wei. Yao and Alan N. Willson, Jr., "A 2.8-3.2-GHz Fractional-N Digital PLL With ADC-Assisted TDC and Inductively Coupled Fine- Tuning DCO,", *IEEE J. of Solid-State Circuits*, vol. 48, no. 3, pp. 698–710, Mar. 2013.

- [32] S. Seo, J. Chun, Y. Jun, S. Kim and K. Kwon, "A Digitally Controlled Oscillator With Wide Frequency Range and Low Supply Sensitivity", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 58, no. 10, pp. 632-636, Oct. 2011.

- [33] J. Bae et al., "A Design of 0.7-V 400-MHz Digitally-Controlled Oscillator," *IEICE TRANS. ELECTRON.*, vol. E98-C, no. 12, pp. 1179–1186, Dec. 2015.

- [34] M. Babaie et al., "A class-F CMOS oscillator," *IEEE J. of Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [35] F. Silveira et al., "A  $g_m/I_D$  based methodology for the design of CMOS analog circuits and its applications to the synthesis of a silicon-oninsulator micropower OTA," *IEEE J. of Solid-State Circuits*, vol. 31, no. 9, pp. 1314–1319, Sept. 1996.

- [36] J. Bae et al., "A Design of 0.7-V 400-MHz Digitally-Controlled Oscillator," *IEICE TRANS. ELECTRON.*, vol. E98-C, no. 12, pp. 1179–1186, Dec. 2015.

- [37] Luca Fanori et al., "Class-D CMOS Oscillators," *IEEE J. of Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [38] H. Lee et al., "A Subthreshold Low Phase Noise CMOS LC VCO for Ultra Low Power Applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 11, pp. 796–798, Nov. 2007.

IMRAN ALI received his B.S. and M.S. degrees in Electrical Engineering from University of Engineering and Technology (UET), Taxila, Pakistan, in 2008 and 2014, respectively. He received his Ph.D. degree in Electronic and Electrical Engineering from Sungkyunkwan University, South Korea in 2020. From 2008 to 2015, he was with Horizon Tech. Services, Islamabad, Pakistan, where he was a Senior

Engineer in the Product Development Division and worked on the design and development of hardware based crypto/non-crypto systems. He is currently Post-Doctoral Research Associate with College of Information and Communication Engineering, Sungkyunkwan University, South Korea. His research interests include digital system design, digital controllers, digital calibration algorithms, artificial intelligence and analog/digital mixed signal integrated circuits.

HAMED ABBASIZADEH received the M.S. degree in electrical and computer engineering from the Azad University of Qazvin, Qazvin, Iran, in 2012, and the Ph.D. degree in electrical and computer engineering from the Sungkyunkwan University, Suwon, Korea, in 2017. He was a Post-Doctoral Researcher with the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, Korea, from 2017 to 2018, working on the design of a

simultaneous wireless information and power transceiver for low-power IoT devices. He was a Post-Doctoral Research Associate with the Biomedical Engineering Department, University of Connecticut, Storrs, CT, USA, from 2018 to 2019, where his research focused on a bidirectional communicated implantable neuro-stimulator device. He is currently a Post-Doctoral Research Associate with the Energy-Efficient Microsystems Lab, Department of Electrical and Computer Engineering, University of California at San Diego (UCSD), La Jolla, CA, USA. His research interests include RF-integrated circuits and power management IC.

MUHAMMAD RIAZ UR REHMAN received his B.S. Computer Engineering and M.S. Electrical Engineering from University of Engineering and Technology, Taxila, Pakistan, in 2007 and 2011, respectively. From 2007 to 2016, he was with Horizon Tech Services, Islamabad, Pakistan, where he was a Senior Engineer of the Product Development Division. He is currently working toward Ph.D. degree in School of Information and Communication Engineering at

Sungkyunkwan University, Suwon, Korea. His research interests include time to digital conversion systems, and embedded and digital systems design.

MUHAMMAD ASIF received his B.S. in Electrical and Electronic Engineering from National University of Modern Languages and Science, Islamabad, Pakistan, in 2013. He completed his M.S in Electrical and Computer Engineering from Sungkyunkwan University, Suwon, South Korea, in 2020. Currently, he is serving as a researcher in Integrated Circuits (IC) Lab at Sungkyunkwan University, Suwon, South Korea. His research interests include implementation of power integrated circuits, analog/digital mixed

circuits and CMOS digital controller.

**SEONGJIN OH** received his B.S. degree from the Department of Electronic Engineering at Sungkyunkwan University, Suwon, Korea, in 2014, where he is currently working toward the Combined Ph.D. & M.S degree in School of Information and Communication Engineering. His research interests include CMOS RF transceiver, All Digital Phase Locked Loop, Wireless Power Transfer Receiver, and Rectifier.

YOUNG GUN PU received his B.S., M.S. and Ph.D. degrees from the Department of Electronic Engineering at Konkuk University, Seoul, South Korea, in 2006, 2008 and 2012, respectively. His research interests include CMOS fully integrated frequency synthesizers and oscillators and on transceivers for low-power mobile communication.

MINJAE LEE received his B.Sc. and M.S. degrees both in Electrical Engineering from Seoul National University, Seoul, Korea in 1998 and 2000 respectively. He received the Ph.D. degree in Electrical Engineering from the University of California, Los Angeles, in 2008. In 2000, he was a consultant with GCT semiconductor, Inc., and Silicon Image Inc., designing analog circuits for wireless communication and digital signal processing blocks for Gigabit

Ethernet. He joined Silicon Image Inc., Sunnyvale, CA in 2001, developing Serial ATA products. In August 2008, he joined Agilent Technologies in Santa Clara, CA, where he was involved with the development of next generation high-speed ADCs and DACs. Since 2012, he has been with the School of Information and Communications, Gwangju Institute of Science and Technology, Gwangju, Korea, where he is now an Assistant Professor. Dr. Lee was the recipient of the 2007 Best Student Paper Award at the VLSI Circuits Symposium in Kyoto, Japan and He received the GIST Distinguished Lecture Award in 2015.

**KEUM CHEOL HWANG** (SM' 13) received his B.S. degree in Electronics Engineering from Pusan National University, Busan, South Korea in 2001 and M.S. and Ph.D. degrees in Electrical and Electronic Engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea in 2003 and 2006, respectively. From 2006 to 2008, he was a Senior Research Engineer at the Samsung Thales, Yongin, South Korea, where he was involved with the

development of various antennas including multiband fractal antennas for communication systems and Cass-grain reflector antenna and slotted waveguide arrays for tracking radars. He was an Associate Professor in the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, South Korea from 2008 to 2014. In 2015, he joined the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, where he is now an Associate Professor. His research interests include advanced electromagnetic scattering and radiation theory and applications, design of multi-band/broadband antennas and radar antennas, and optimization algorithms for electro-magnetic applications. Dr. Hwang is a Life-Member of KIEES, a senior member of IEEE and a member of IEICE.

YOUNGOO YANG (SM' 15) was born in Hamyang, Korea, in 1969. He received the Ph.D. degree in electrical and electronic engineering from the Pohang University of Science and Technology (Postech), Pohang, Korea, in 2002. From 2002 to 2005, he was with Skyworks Solutions Inc., Newbury Park, CA, where he designed power amplifiers for various cellular handsets. Since March 2005, he has been with the School of Information and Communication

Engineering, Sungkyunkwan University, Suwon, Korea, where he is currently an Associate Professor. His research interests include power amplifier design, RF transmitters, RFIC design, integrated circuit design for RFID/USN systems, and modeling of high power amplifiers or devices.

KANG-YOON LEE (SM' 12) received the B.S., M.S. and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA, USA where he was a Manager of the Analog Division and worked on the design of CMOS frequency synthesizer for CDMA/PCS/PDC and single-chip CMOS RF chip sets for W-CDMA,

WLAN, and PHS. From 2005 to 2011, he was with the Department of Electronics Engineering, Konkuk University as an Associate Professor. Since 2012, he has been with College of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently a Professor. His research interests include implementation of power integrated circuits, CMOS RF transceiver, analog integrated circuits, and analog/digital mixed-mode VLSI system design.